|

Red_TsnEndNode_Flyer.pdf Size : 150.175 Kb Type : pdf |

|

Red_TsnEndNode_ReferenceManual.pdf Size : 2857.861 Kb Type : pdf |

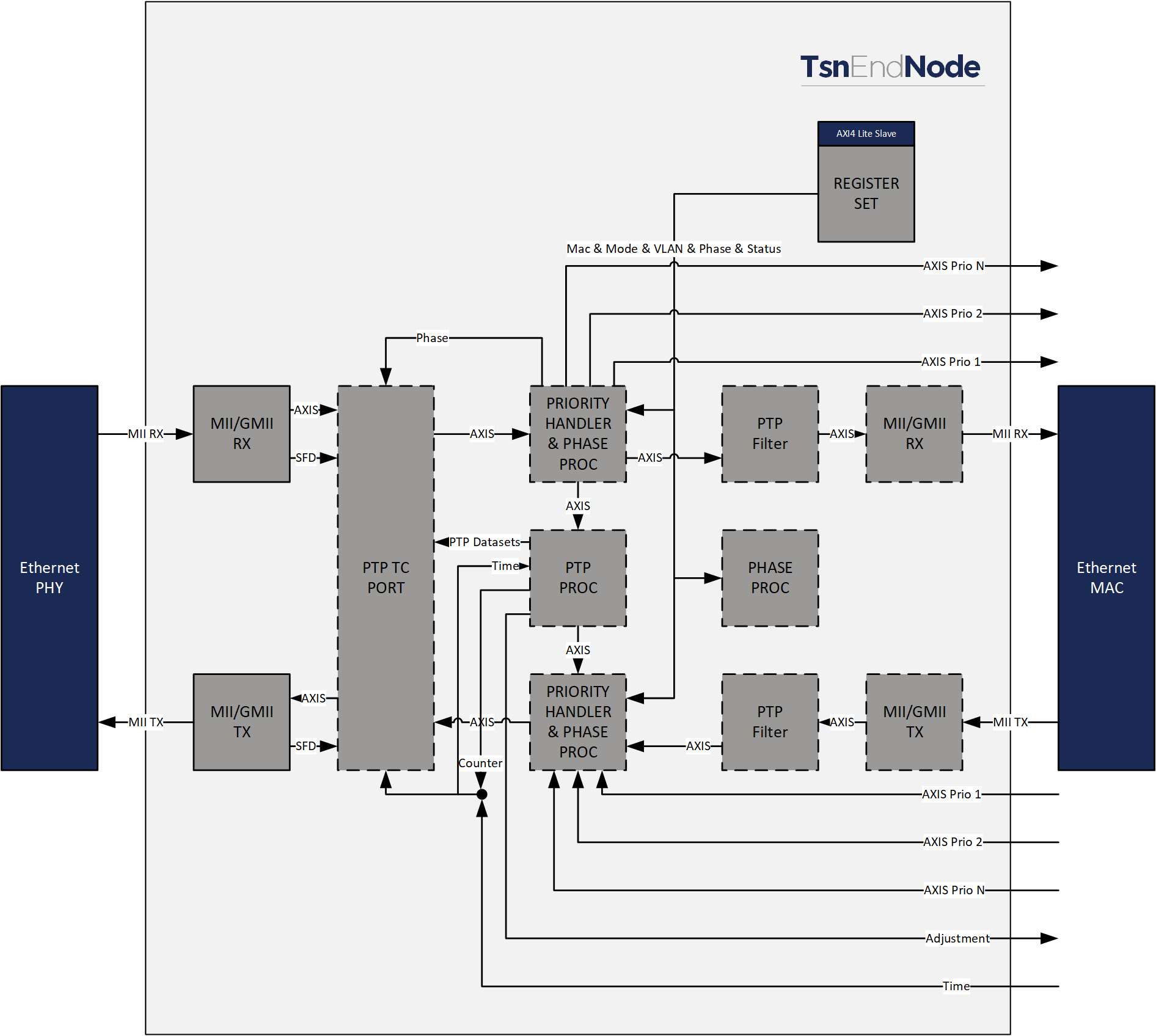

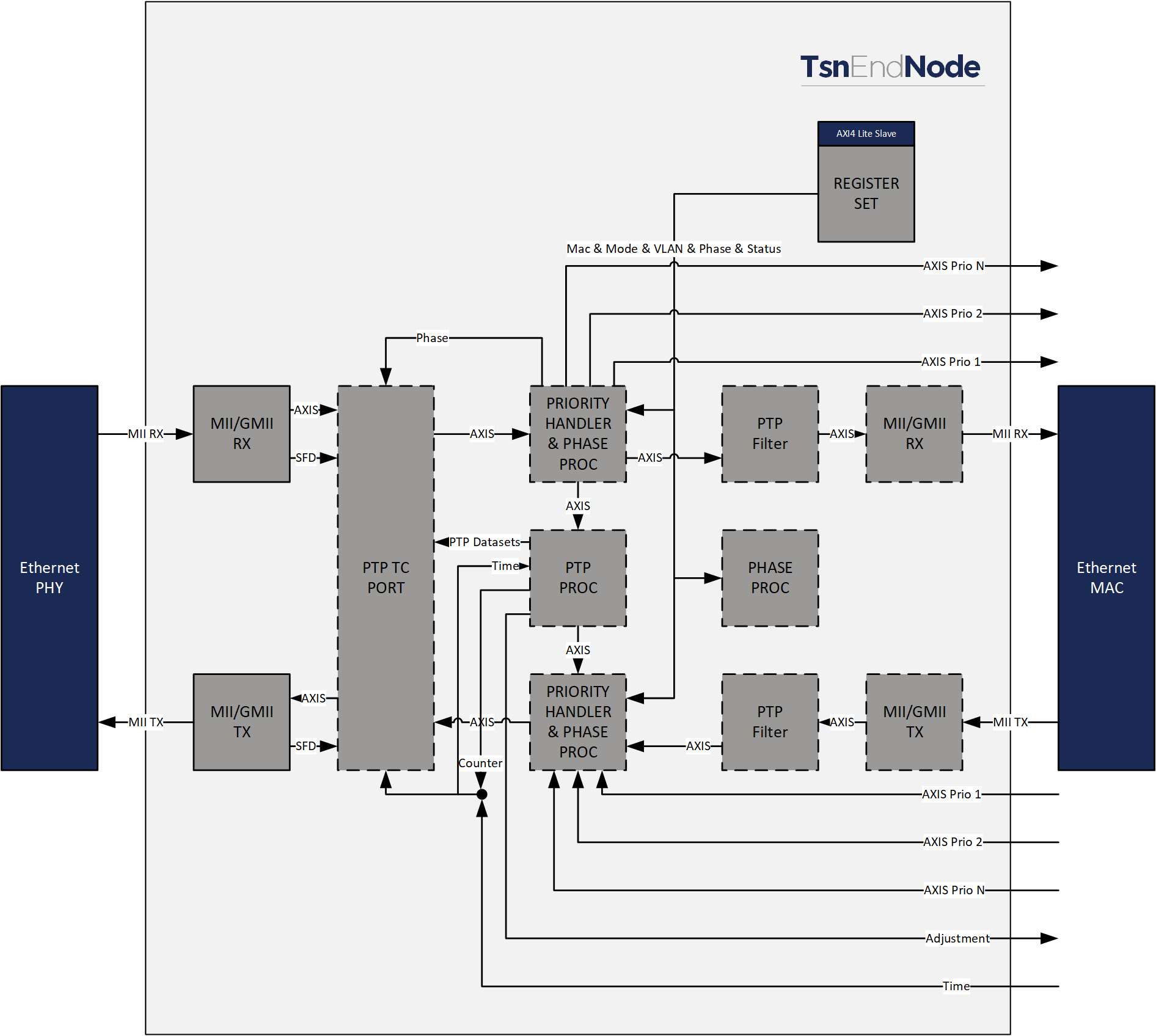

The TSN End Node IP core from NetTimeLogic is a standalone Time Sensitive Networking (TSN) single port end node core according to IEEE 802.1 and IEEE 1588 standards. It supports the same features as the TSN Network Node (switched endpoint) core except network redundancy. It is meant as a TSN co-processor enabling non-TSN aware interfaces (e.g. legacy or "normal"MAC) to support TSN features like scheduling, priority queues, credit shaping, cyclic forwarding and preemption. The core is intercepting the path between the Ethernet PHY and an Ethernet core that forwards or handles Ethernet frames (MAC, PHY or Switch). In addition, it has up to 8 streaming ports which allow to send and receive frames directly from the specific priority queues and phases.

All tables, protocols and algorithms are implemented completely in HW in the core, no CPU is required, except for configuration. This allows running TSN protocols completely independent and standalone from the user application.

Can be combined with the IIC(R) Plugfest Application IP core or OPC-UA stack like Open62541.

There are different licensing possibilities (more info here). All prices are in US Dollars without VAT, all prices are one-time fees, no royalties apply:

All prices are non-binding estimates – please use the contact form for definitive pricing and lead-time information.

|

Red_TsnEndNode_Flyer.pdf Size : 150.175 Kb Type : pdf |

|

Red_TsnEndNode_ReferenceManual.pdf Size : 2857.861 Kb Type : pdf |