|

Ucm_UniversalConfigurationManager_QuickstartGuide.pdf Size : 403.047 Kb Type : pdf |

|

Ucm_UniversalConfigurationManager_ReferenceManual.pdf Size : 273.106 Kb Type : pdf |

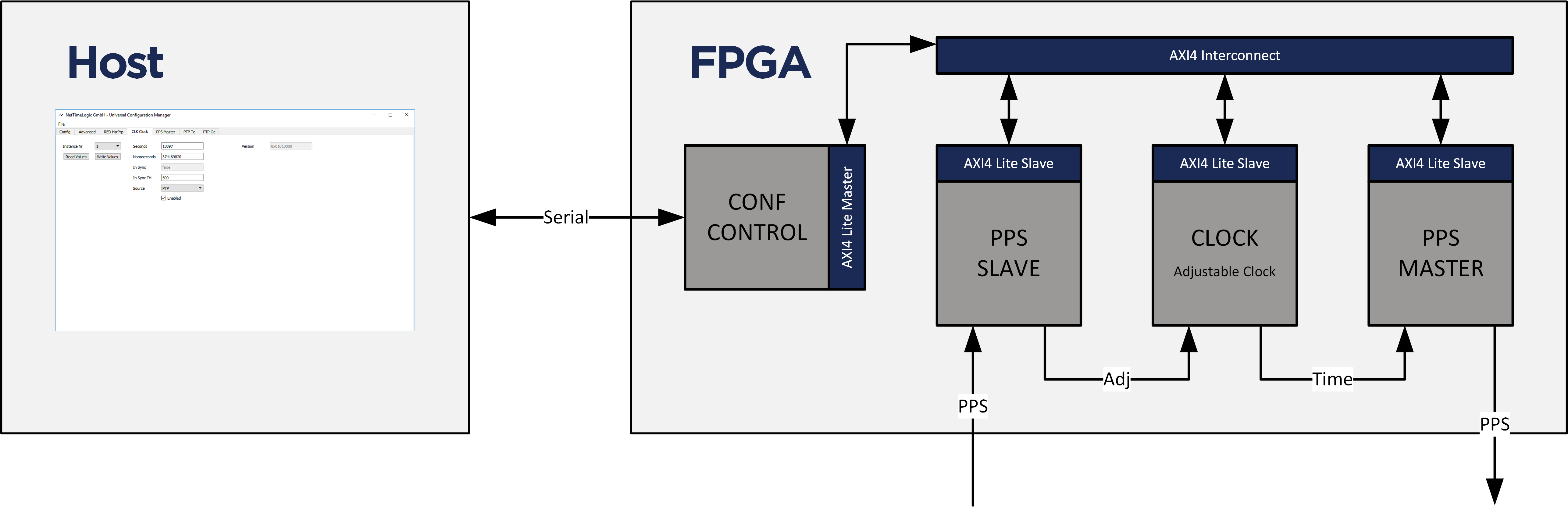

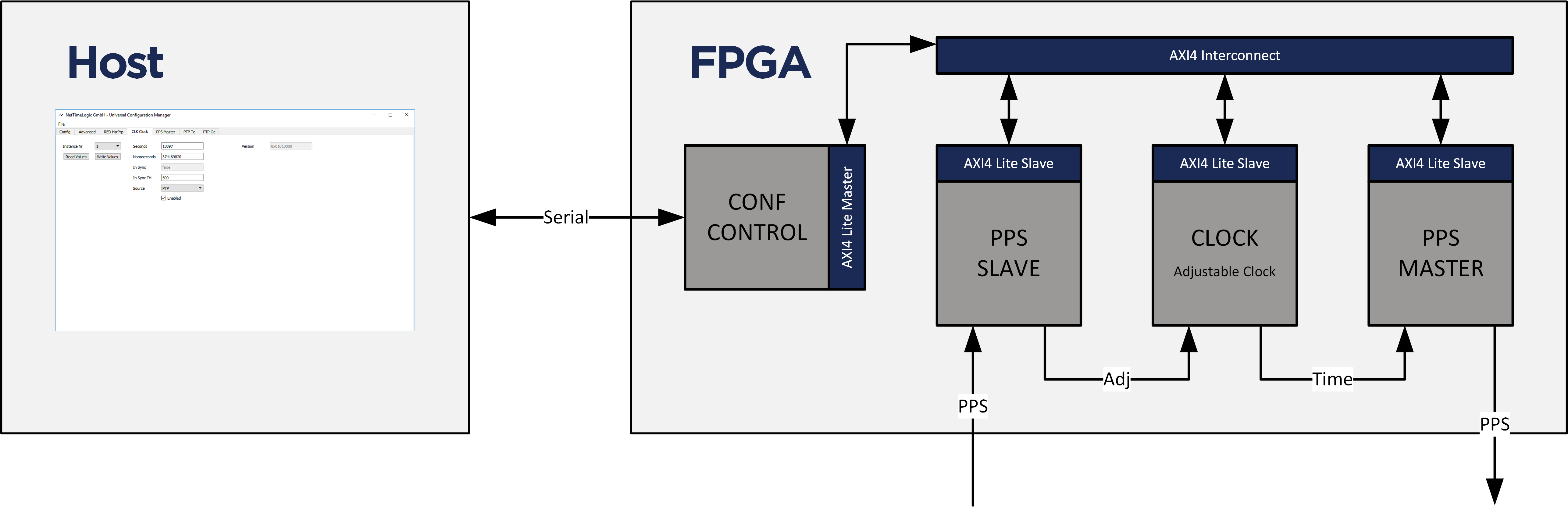

NetTimeLogic's Universal Configuration Manager is a complete configuration solution that allows to configure, manage and supervise all IP cores from NetTimeLogic in an FPGA. It uses a serial interface (mostly over USB) or Ethernet to access the registers in the FPGA. In the FPGA it uses NetTimeLogic's configuration IP (free of charge) which represents an AXI Master to the other IP cores. It uses a proprietary protocol to convert the serial data stream from/to AXI register access. The tool needs no configuration and self-discovers all cores available in the design. It allows to access all registers in the design (also third party) which are connected to the AXI bus. Multiple instances of the application can run in parallel and access one board each.

The application is written with Qt as GUI framework and is currently available for Windows

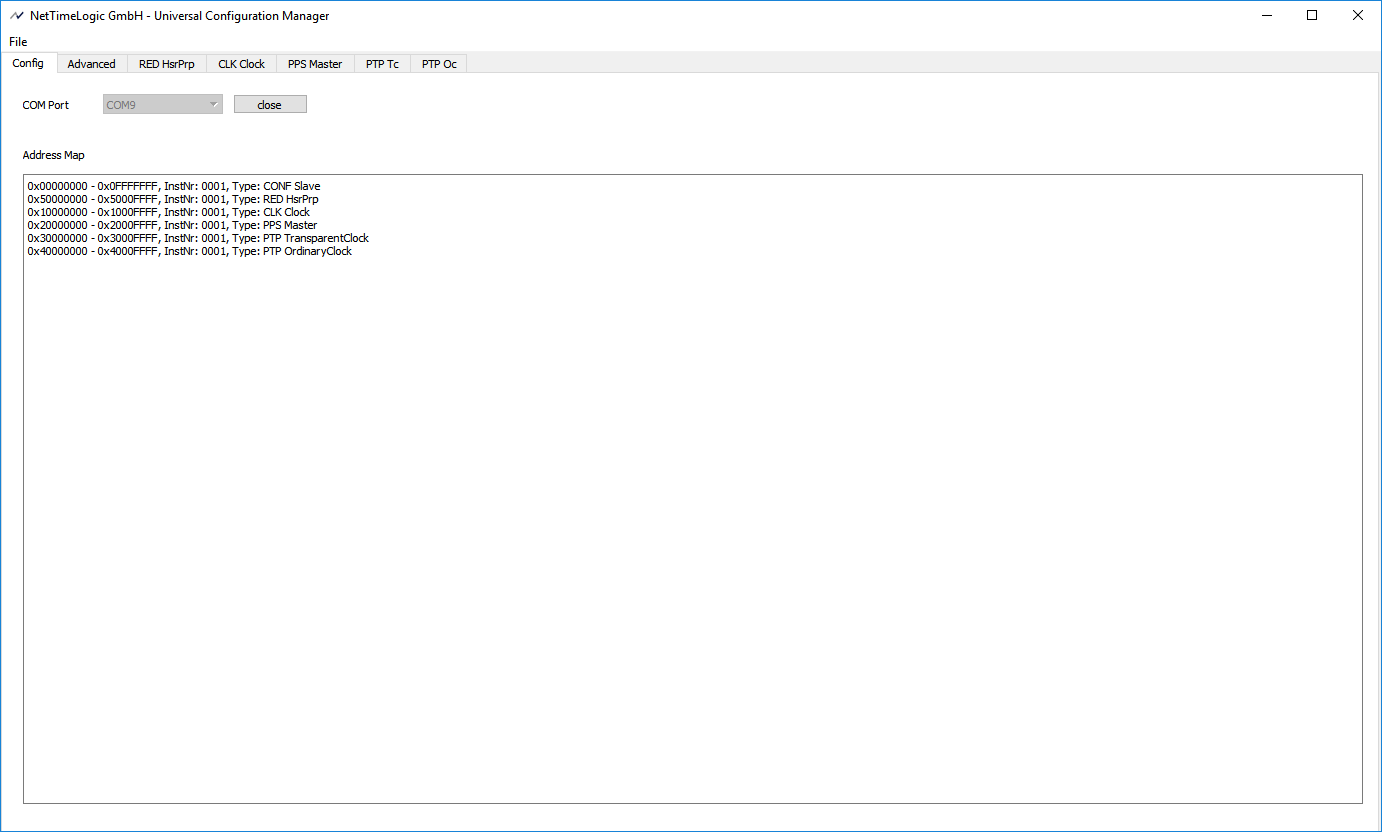

This is an example of a design with three cores. (This is only an example and can be changed to any other configuration.)

Free of charge, licensed under LGPL

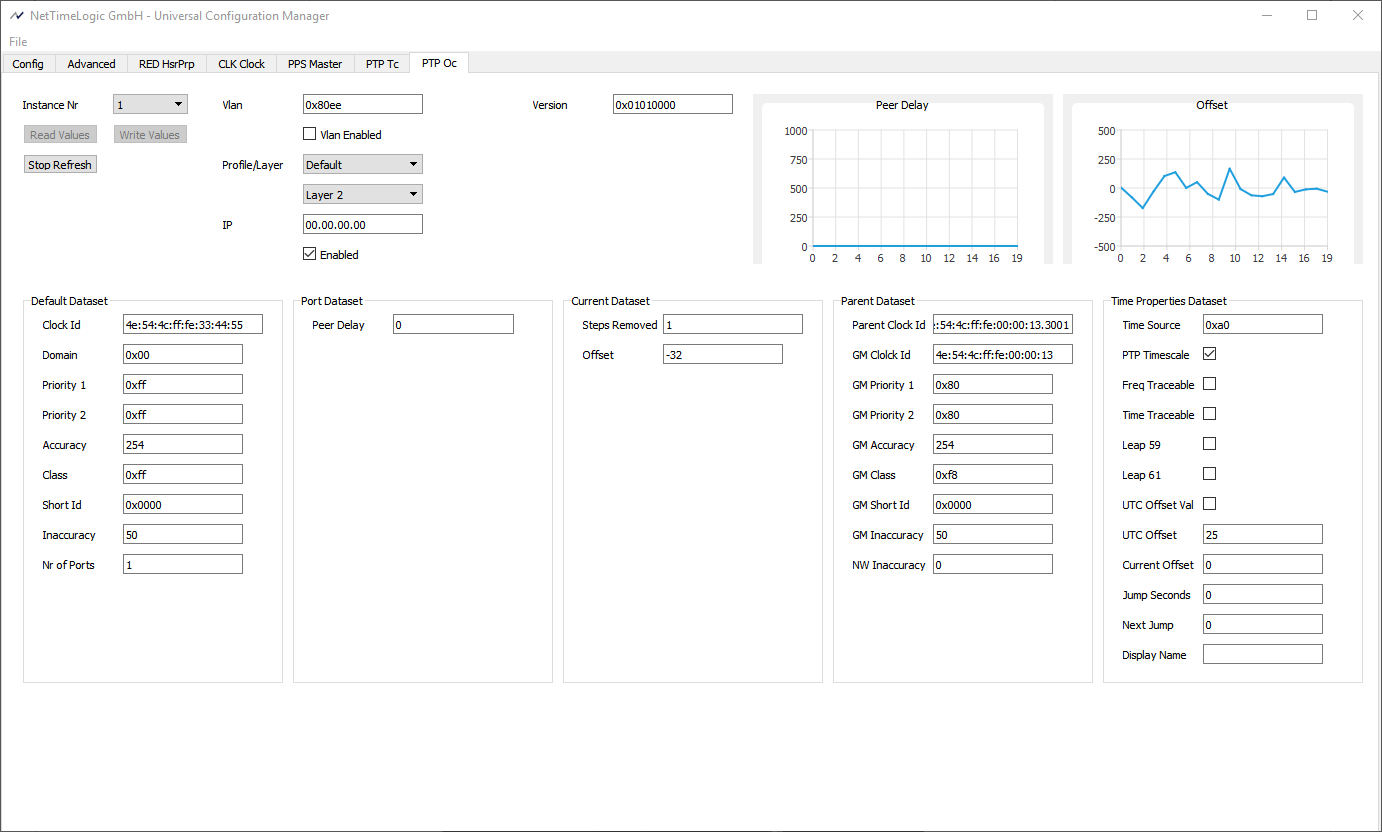

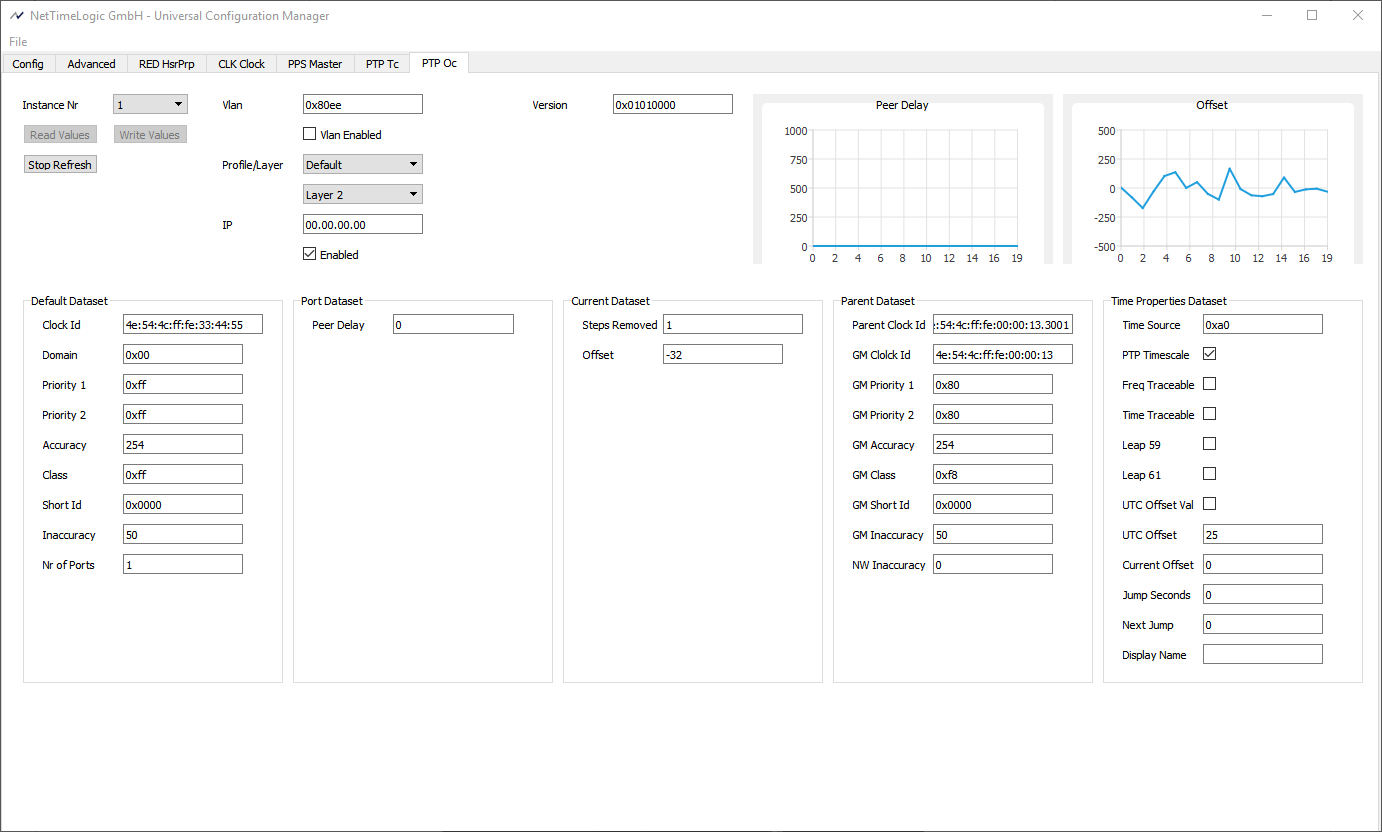

PTP Ordinary Clock IP core screen, allowing to access the PTP data sets and monitoring the calculated offset and delay in real time (here constant zero because of internal measurement)

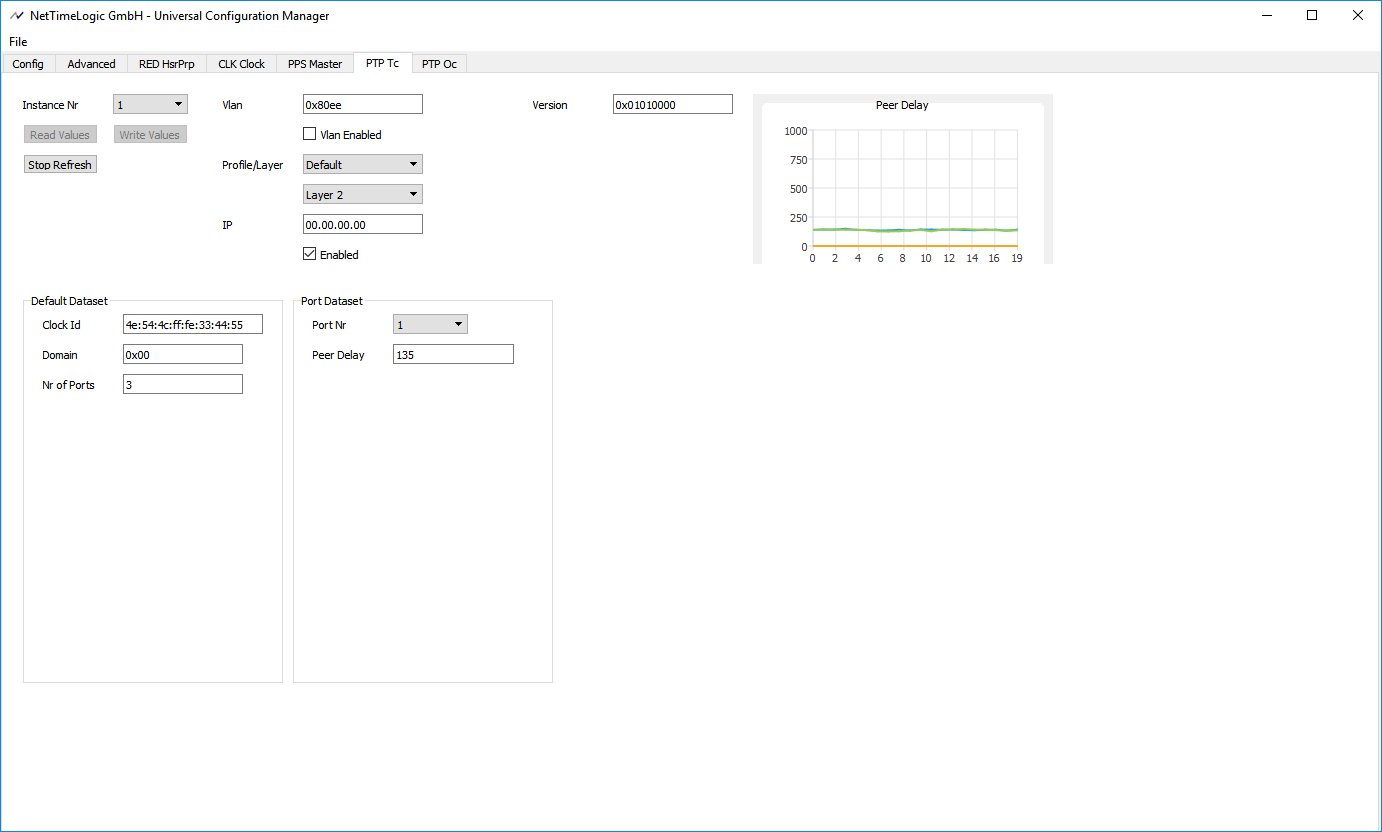

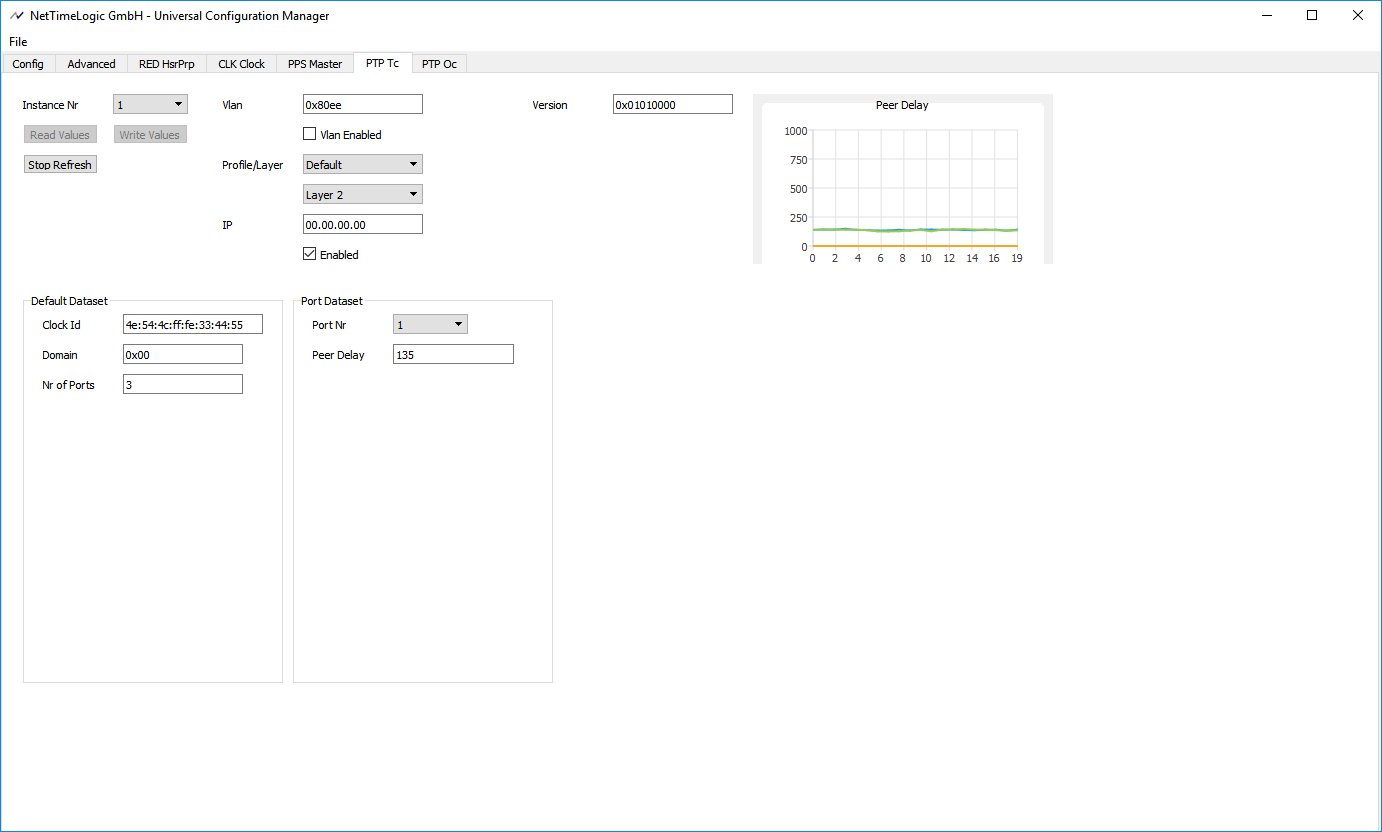

PTP Transparent Clock IP core screen, allowing to access the PTP data sets and monitoring the delay in real time of all ports (third port here constant zero because of internal measurement)

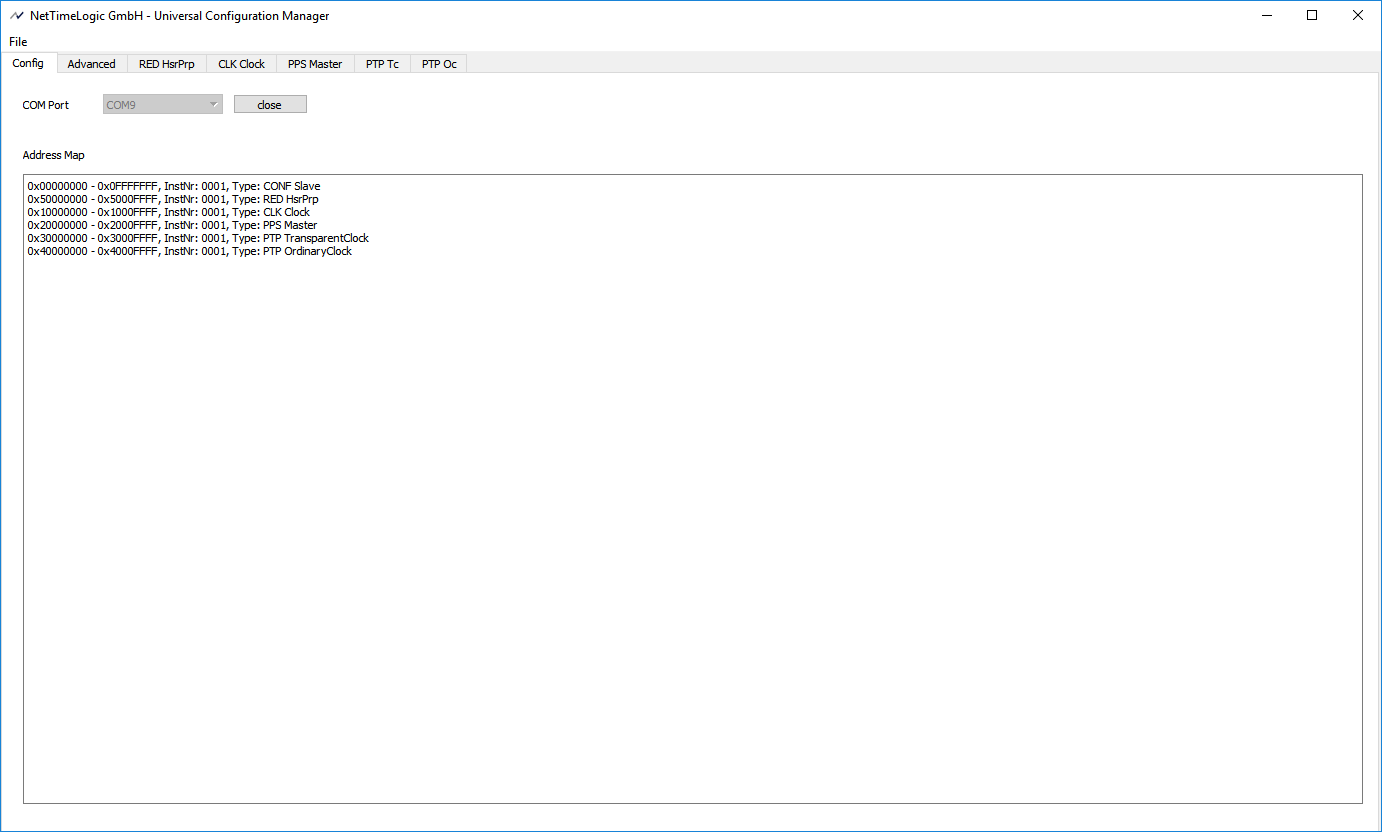

Configuration screen showing the address map of the available cores.

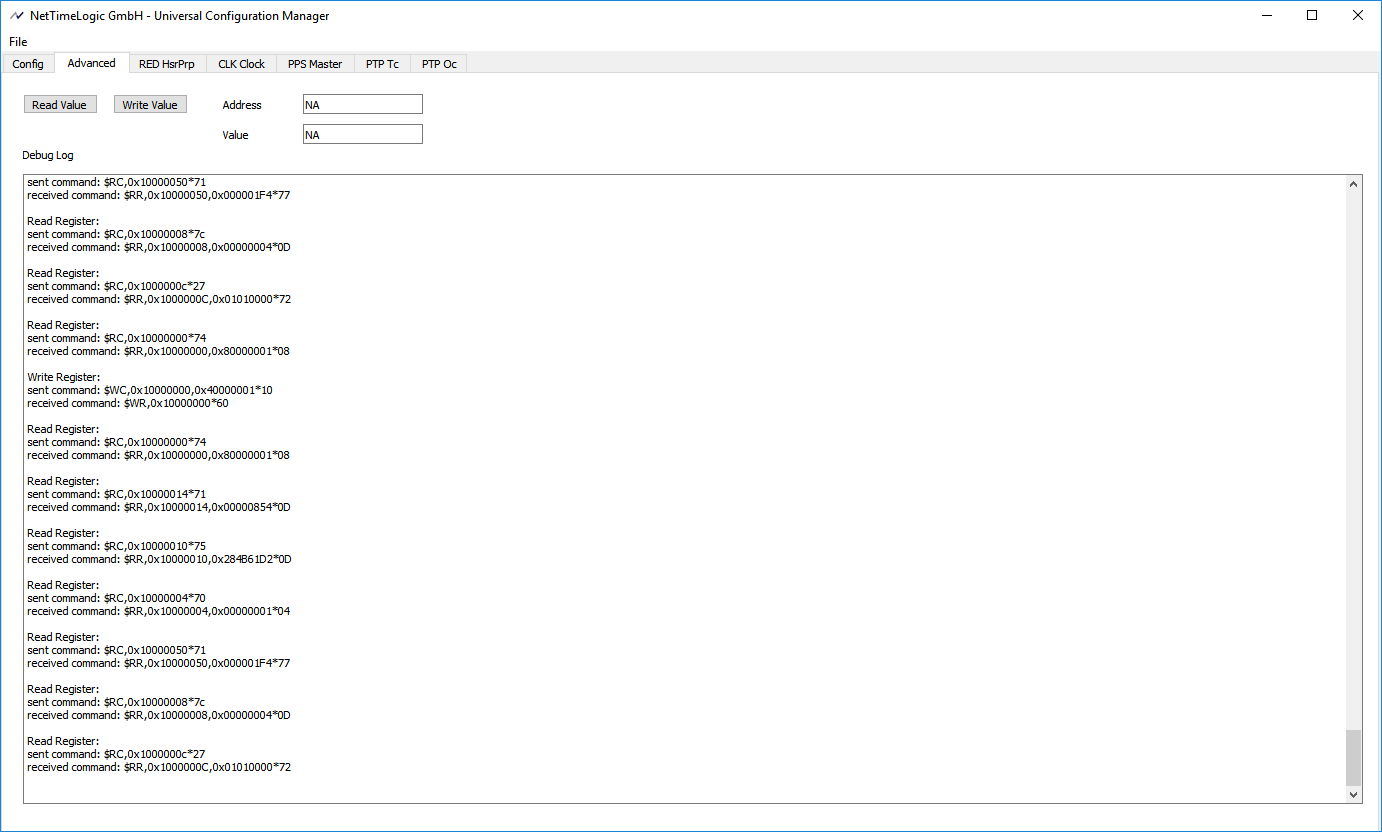

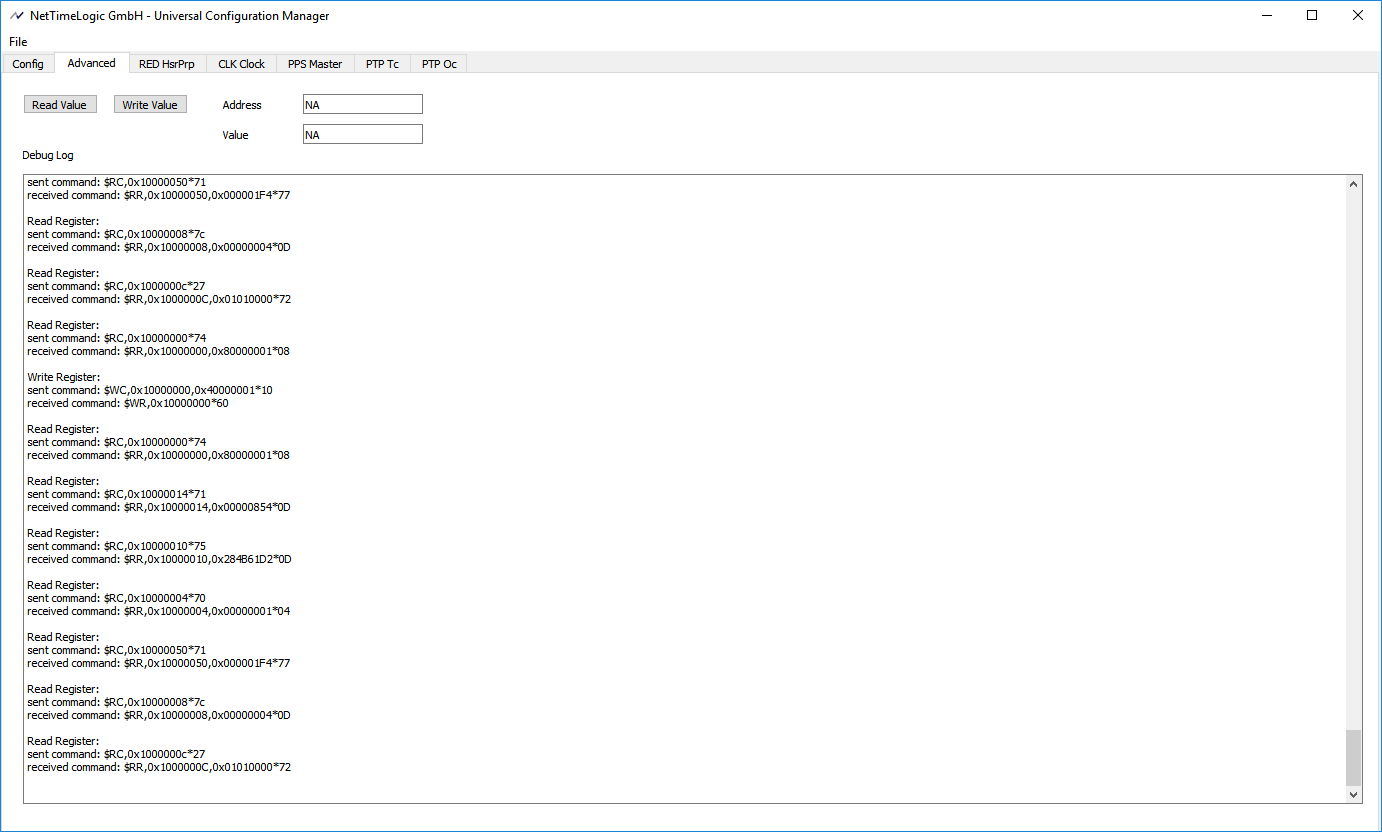

Advanced screen allowing to read and write to any AXI address.

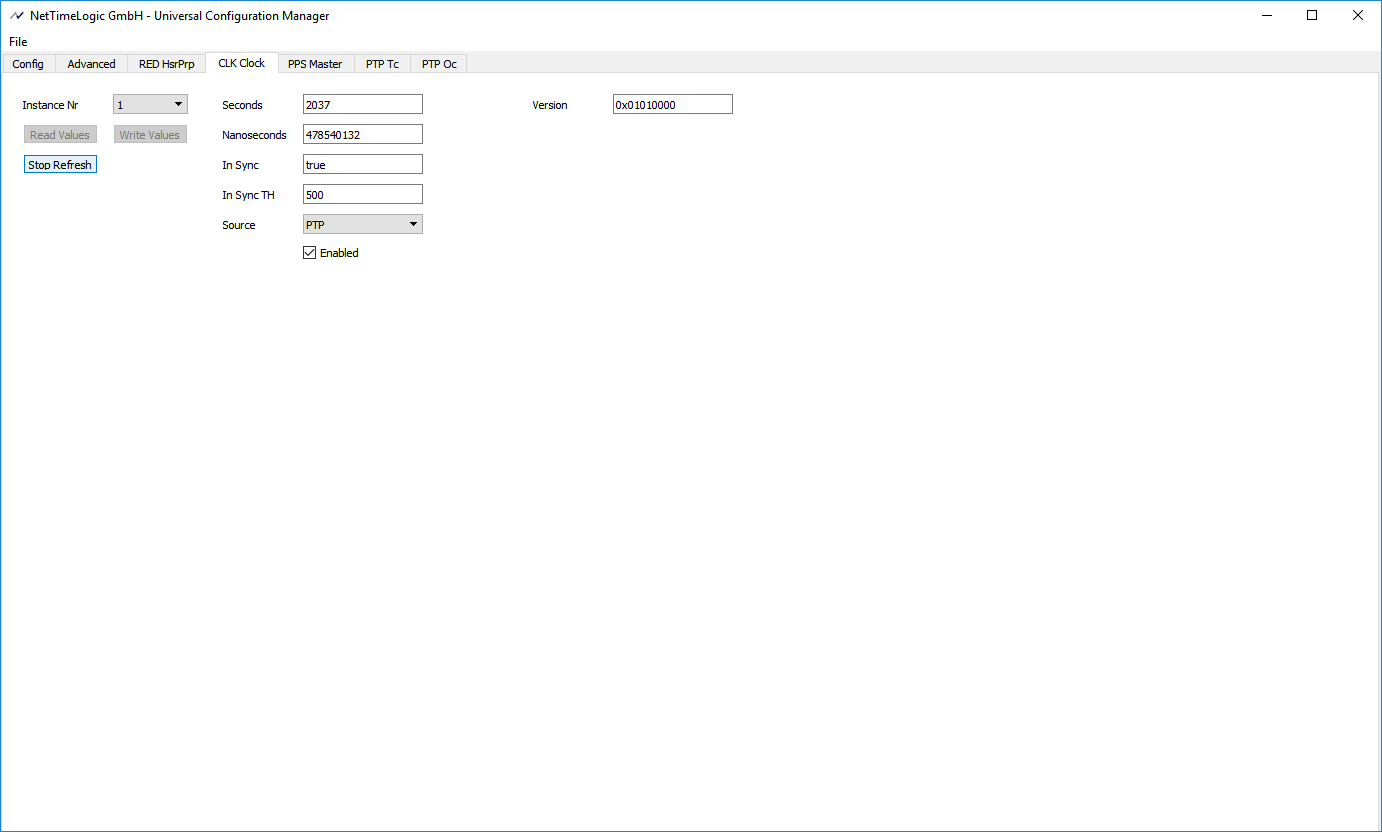

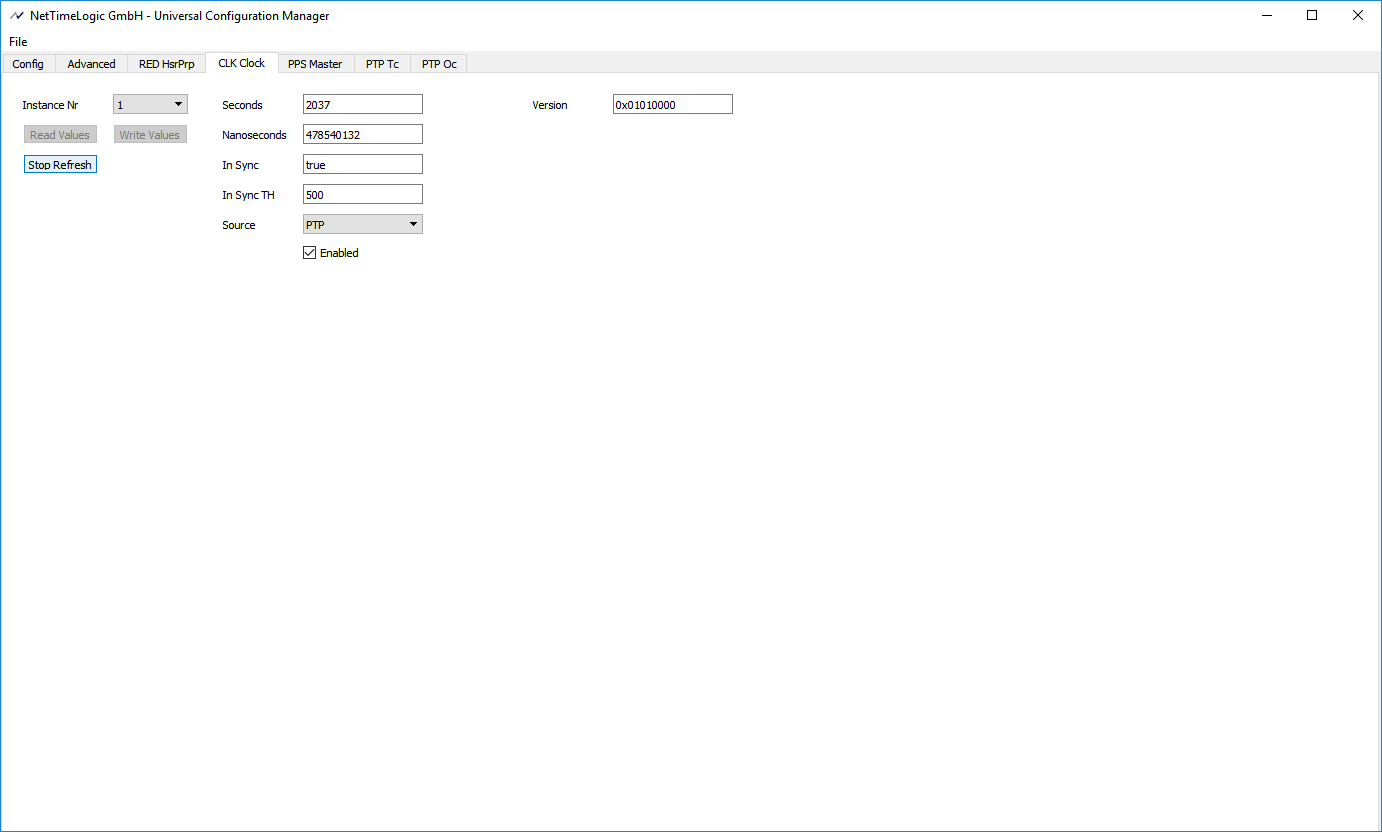

Clock IP core screen, allowing to read/write the time and check the status.

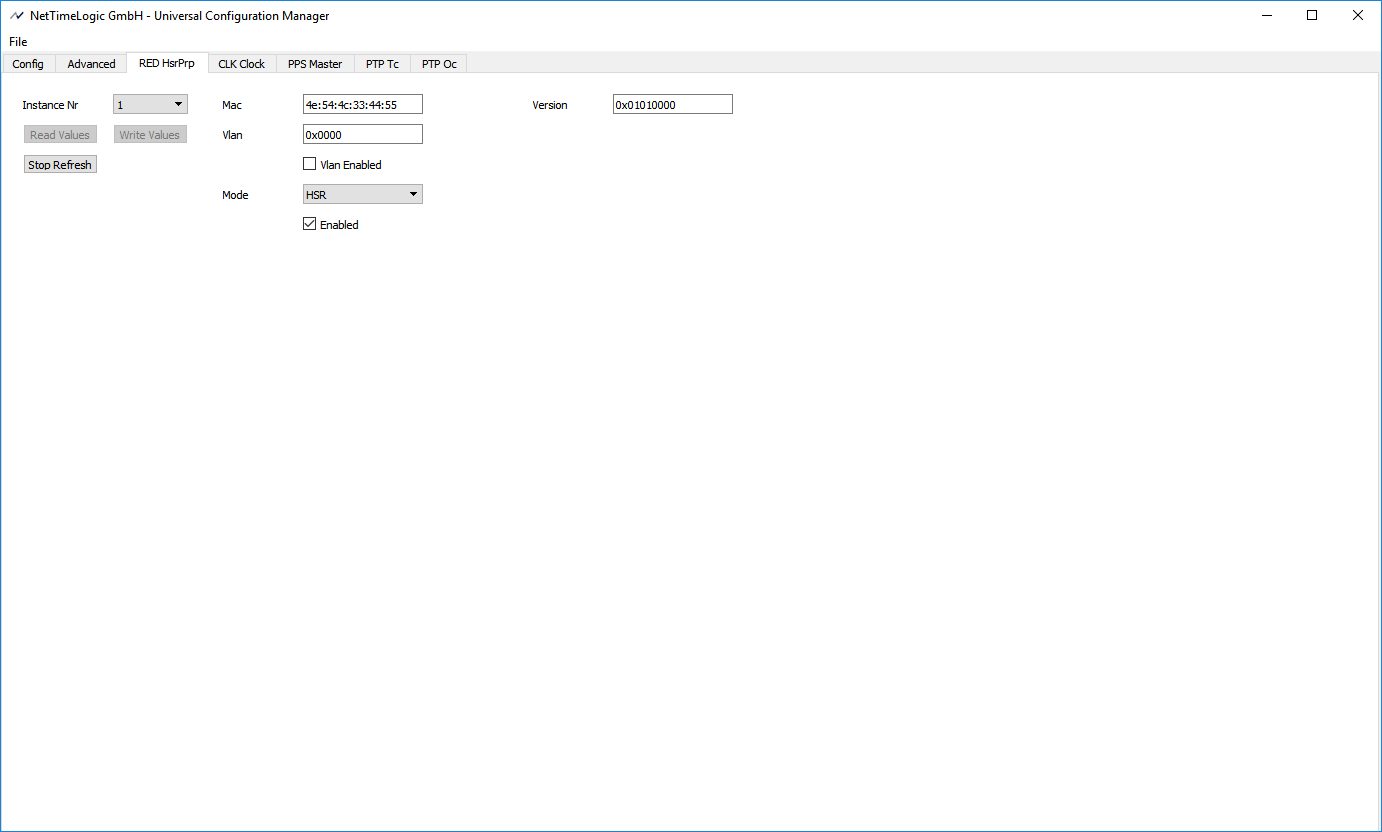

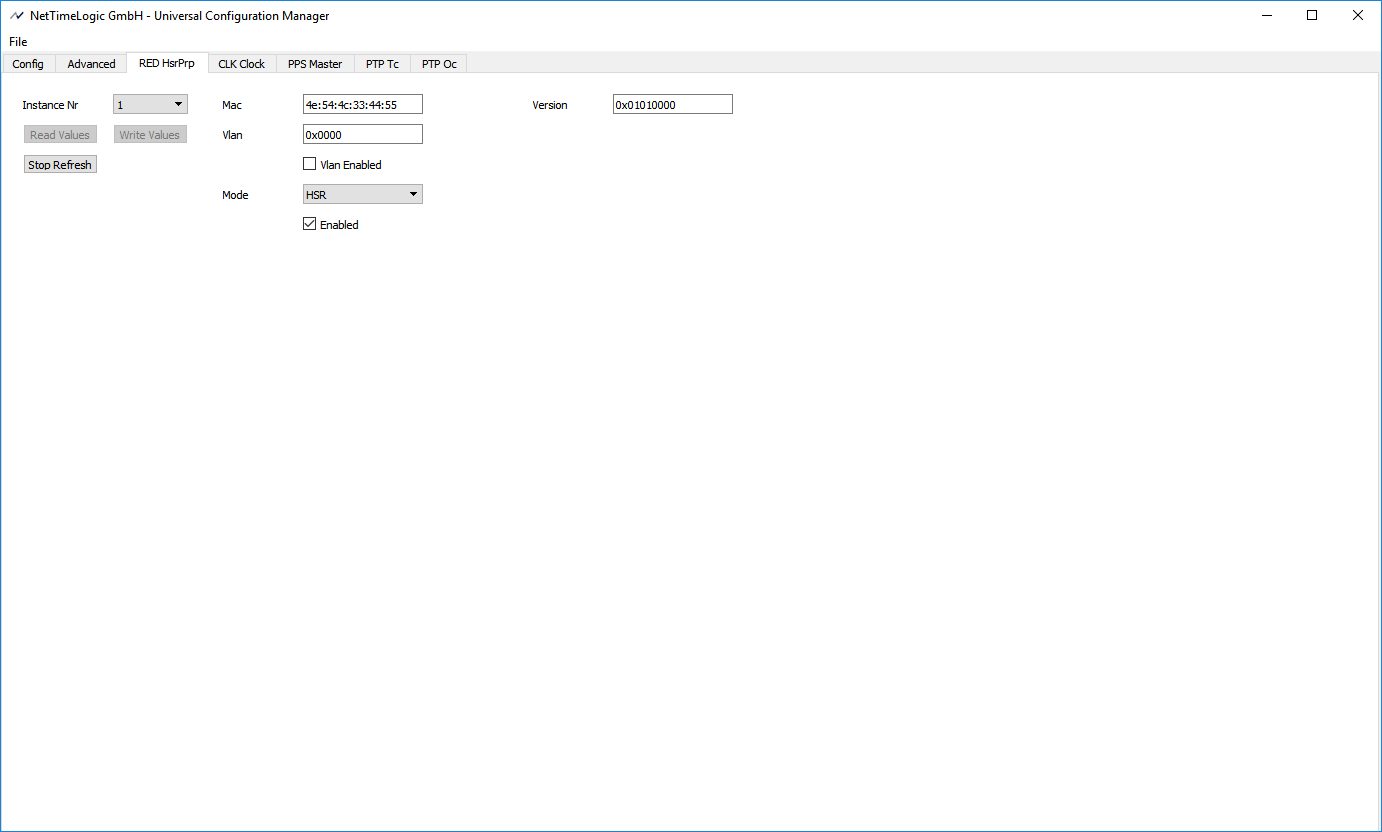

Redundancy IP core screen, allowing to read/write the MAC and redundancy mode and check the status.

|

Ucm_UniversalConfigurationManager_QuickstartGuide.pdf Size : 403.047 Kb Type : pdf |

|

Ucm_UniversalConfigurationManager_ReferenceManual.pdf Size : 273.106 Kb Type : pdf |

The whole project can be found as sources on NetTimeLogic's Open SourceGithub account:

https://github.com/NetTimeLogic-OpenSource/UniversalConfigurationManager

Contact us if you would like to contribute to the development of this open source project