|

Red_HsrPrp_Flyer.pdf Size : 150.681 Kb Type : pdf |

|

Red_HsrPrp_ReferenceManual.pdf Size : 1196.452 Kb Type : pdf |

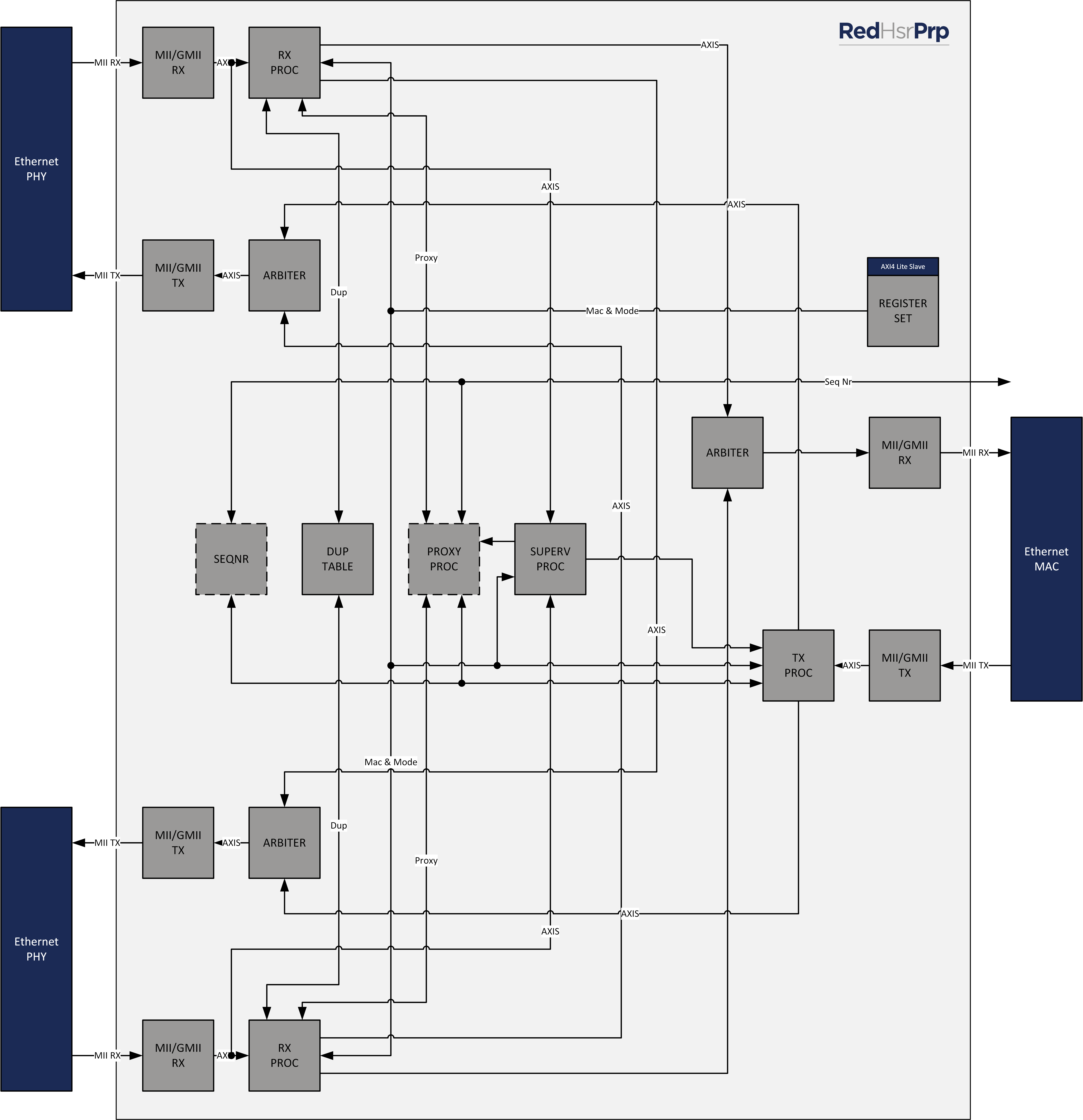

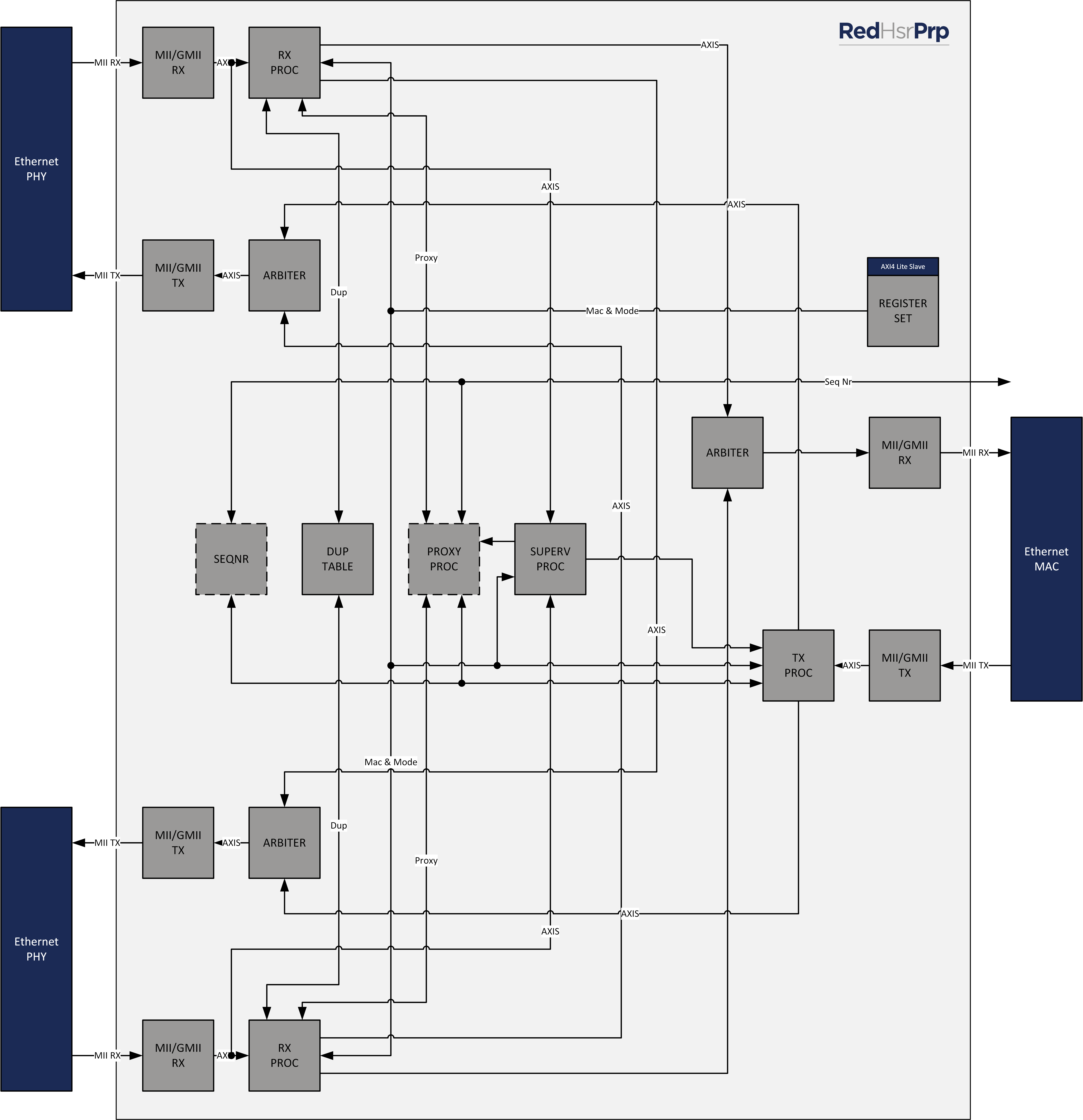

The HSR&PRP Core from NetTimeLogic is a standalone Network Redundancy Core according to IEC62439-3 rev3. It allows to connect to a redundant network supporting either the Parallel Redundancy Protocol (PRP) or the High-availability Seamless Redundancy Protocol (HSR). It can either run as a Dual Attached Node (DAN) being an endpoint or it can run as a Redundancy Box (RedBox) bridging between a redundant and a non-redundant network.

The core has three ports: A redundant pair named Ports A&B and an uplink named Port C. The basic principal is duplicating and tagging frames on the path from Port C to Ports A&B and duplicate rejection and untagging on the path from Ports A&B to Port C. It can support a configurable number of nodes on the redundant side and also on the non-redundant network (when run as RedBox). It makes a basic supervision of the redundant network and sends supervision frames for its non-redundant connected nodes. The Core learns the connected nodes (MACs) itself and needs no further configuration.

The HSR&PRP Core is intercepting the path between two Ethernet PHYs and an Ethernet core that forwards or handles Ethernet frames (MAC or Switch).

All tables, protocols and algorithms are implemented completely in HW.

There are different licensing possibilities (more info here). All prices are in US Dollars without VAT, all prices are one-time fees, no royalties apply:

All prices are non-binding estimates – please use the contact form for definitive pricing and lead-time information.

Evaluation binaries available for Digilent NetFPGA development boards or as Modelsim(R) precompiled libraries => contact us for free access

|

Red_HsrPrp_Flyer.pdf Size : 150.681 Kb Type : pdf |

|

Red_HsrPrp_ReferenceManual.pdf Size : 1196.452 Kb Type : pdf |