# RedHsrPrp

# Reference Manual

| Product Info    |            |

|-----------------|------------|

| Product Manager | Sven Meier |

| Author(s)       | Sven Meier |

| Reviewer(s)     | -          |

| Version         | 5          |

| Date            | 03.01.2023 |

# **Copyright Notice**

Copyright © 2025 NetTimeLogic GmbH, Switzerland. All rights reserved. Unauthorized duplication of this document, in whole or in part, by any means, is prohibited without the prior written permission of NetTimeLogic GmbH, Switzerland.

All referenced registered marks and trademarks are the property of their respective owners

## Disclaimer

The information available to you in this document/code may contain errors and is subject to periods of interruption. While NetTimeLogic GmbH does its best to maintain the information it offers in the document/code, it cannot be held responsible for any errors, defects, lost profits, or other consequential damages arising from the use of this document/code.

NETTIMELOGIC GMBH PROVIDES THE INFORMATION, SERVICES AND PRODUCTS AVAILABLE IN THIS DOCUMENT/CODE "AS IS," WITH NO WARRANTIES WHATSOEVER. ALL EXPRESS WARRANTIES AND ALL IMPLIED WARRANTIES, INCLUDING WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF PROPRIETARY RIGHTS ARE HEREBY DISCLAIMED TO THE FULLEST EXTENT PERMITTED BY LAW. IN NO EVENT SHALL NETTIMELOGIC GMBH BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, CONSEQUENTIAL, SPECIAL AND EXEMPLARY DAMAGES, OR ANY DAMAGES WHATSOEVER, ARISING FROM THE USE OR PERFORMANCE OF THIS DOCUMENT/CODE OR FROM ANY INFORMATION, SERVICES OR PRODUCTS PROVIDED THROUGH THIS DOCUMENT/CODE, EVEN IF NETTIMELOGIC GMBH HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

IF YOU ARE DISSATISFIED WITH THIS DOCUMENT/CODE, OR ANY PORTION THEREOF, YOUR EXCLUSIVE REMEDY SHALL BE TO CEASE USING THE DOCUMENT/CODE.

## Overview

The HSR&PRP Core from NetTimeLogic is a standalone Network Redundancy Core according to IEC62439-3 rev3. It allows to connect to a redundant network supporting either the Parallel Redundancy Protocol (PRP) or the High-availability Seamless Redundancy Protocol (HSR). It can either run as a Dual Attached Node (DAN) being an endpoint or it can run as a Redundancy Box (RedBox) bridging between a redundant and a non-redundant network.

The core has three ports: A redundant pair named Ports A&B and an uplink named Port C. The basic principal is the same for both protocols: duplicating and tagging frames on the path from Port C to Ports A&B and duplicate rejection and untagging on the path from Ports A&B to Port C. It can support a configurable number of nodes on the redundant side and also on the non-redundant network (when run as a RedBox). It makes a basic supervision of the redundant network and sends supervision frames for its non-redundant connected nodes. The core learns the connected nodes itself and needs no further configuration.

The HSR&PRP Core is intercepting the path between two Ethernet PHYs and an Ethernet core that forwards or handles Ethernet frames (MAC or Switch).

All tables, protocols and algorithms are implemented in the core, no CPU is required. This allows running network redundancy completely independent and standalone from the user application. The core can be configured either by signals or by an AXI4Lite-Slave Register interface.

# **Key Features:**

- Supports the HSR and PRP redundancy protocol according to IEC62439-3 rev 3

- Can run as Dual Attached Node (DAN) or as Redundancy Box (RedBox)

- Supports HSR Mode H and Mode X and PRP Duplicate Discard Mode

- PTP aware for use with PTP Utility Profile

- Intercepts path between MAC and two PHYs (DAN) or three PHYs (RedBox)

- Configurable number of nodes supported on Port C and Promiscuous Mode

- Full line speed

- AXI4Lite register set or static configuration

- MII/RMII/GMII/RGMII Interface support

- Hardware supervision handling

- Optional frame and error counters per Port

- Optional VLAN tagging and filtering

- Optional Tail Tagging mode

- Optional cut through frame processing

- Optional HSR-PRP or HSR-HSR RedBox mode support

# **Revision History**

This table shows the revision history of this document.

| Version | Date       | Revision                                                                    |

|---------|------------|-----------------------------------------------------------------------------|

| 0.1     | 16.06.2017 | First draft                                                                 |

| 1.0     | 28.07.2017 | First release                                                               |

| 1.1     | 17.08.2017 | NO mode added                                                               |

| 2.0     | 24.07.2018 | Adaptations after merge with TSN and added Port Status and Promiscuous Mode |

| 2.1     | 14.09.2018 | Reworked and Link added                                                     |

| 2.2     | 11.12.2018 | VLAN mode changed, tail tagging added and PRP untagging as option           |

| 2.3     | 07.08.2019 | HSR-PRP and HSR-HSR Mode added                                              |

| 2.4     | 27.02.2020 | Added cut through mode                                                      |

| 2.5     | 03.01.2023 | Added Vivado upgrade version description                                    |

Table 1: Revision History

# Content

| 1                                                                           | INTRODUCTION                                | 10                                                 |

|-----------------------------------------------------------------------------|---------------------------------------------|----------------------------------------------------|

| 1.1                                                                         | Context Overview                            | 10                                                 |

| 1.2                                                                         | Function                                    | 11                                                 |

| 1.3                                                                         | Architecture                                | 11                                                 |

| 1.4                                                                         | Deviations from the Standard or Limitations | 14                                                 |

| 2                                                                           | PRP, HSR AND TAIL TAGGING BASICS            | 15                                                 |

| 2.1<br>2.1.1<br>2.1.2<br>2.1.3<br>2.1.4<br>2.1.5<br>2.1.6<br>2.1.7<br>2.1.8 | HSR NO DAN VDAN SAN RedBox                  | 15<br>15<br>17<br>19<br>19<br>19<br>20<br>20<br>21 |

| 3.1                                                                         | Register Overview                           | 22                                                 |

| 3.2<br>3.2.2<br>3.2.2                                                       |                                             | 24<br>24<br>37                                     |

| 4                                                                           | DESIGN DESCRIPTION                          | 40                                                 |

| 4.1                                                                         | Top Level - RED HsrPrp                      | 40                                                 |

| 4.2.<br>4.2.<br>4.2.                                                        |                                             | 54<br>54<br>60                                     |

| 4.2 | 2.3 Proxy Node Processor       | 67 |

|-----|--------------------------------|----|

| 4.2 | 2.4 Duplicate Processor        | 70 |

| 4.2 | 2.5 Supervision Processor      | 73 |

| 4.2 | 2.6 Sequence Number Processor  | 77 |

| 4.2 | 2.7 Ethernet Interface Adapter | 79 |

| 4.2 | 2.8 Registerset                | 82 |

| 4.3 | Configuration example          | 87 |

| 4.3 | 3.1 Static Configuration       | 87 |

| 4.3 | 3.2 AXI Configuration          | 87 |

| 4.4 | Clocking and Reset Concept     | 89 |

| 4.4 | 4.1 Clocking                   | 89 |

| 4.4 | 4.2 Reset                      | 89 |

| _   |                                | 01 |

| 5   | RESOURCE USAGE                 | 91 |

| 5.1 | Intel/Altera (Cyclone V)       | 91 |

| 5.2 | AMD/Xilinx (Kintex 7)          | 91 |

|     |                                |    |

| 6   | DELIVERY STRUCTURE             | 92 |

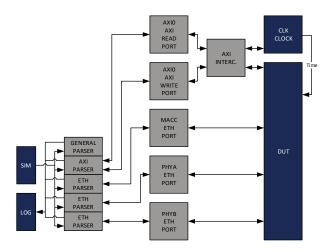

| 7   | TESTBENCH                      | 93 |

| 7.1 | Run Testbench                  | 93 |

|     |                                |    |

| 8   | REFERENCE DESIGNS              | 94 |

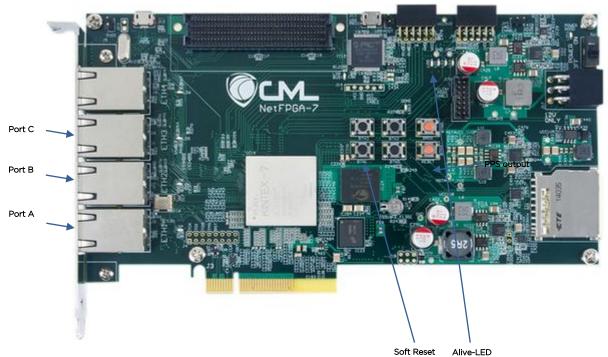

| 8.1 | AMD/Xilinx: Digilent NetFpga   | 94 |

| 8.2 | AMD/Xilinx: Vivado version     | 95 |

|     |                                |    |

# **Definitions**

| Definitions                     |                                                                |

|---------------------------------|----------------------------------------------------------------|

| Redundancy Box                  | Redundancy Box according to IEC62439-3                         |

| Single Attached<br>Node         | A node that does not support redundancy                        |

| Dual Attached<br>Node           | A node that does support redundancy with HSR or PRP            |

| Virtual Dual At-<br>tached Node | A node connected via a Redundancy Box to the redundant network |

Table 2: Definitions

# **Abbreviations**

| Abbreviations |                                                                        |

|---------------|------------------------------------------------------------------------|

| AXI           | AMBA4 Specification (Stream and Memory Mapped)                         |

| IRQ           | Interrupt, Signaling to e.g. a CPU                                     |

| SAN           | Single Attached Node                                                   |

| DAN           | Dual Attached Node                                                     |

| VDAN          | Virtual DAN                                                            |

| RedBox        | Redundancy Box                                                         |

| QuadBox       | Two RedBoxes bridging between two redundant Networks                   |

| PTP           | Precision Time Protocol according to IEEE1588                          |

| PRP           | Parallel Redundancy Protocol according to IEC62439-3                   |

| HSR           | High-availability Seamless Redundancy Protocol according to IEC62439-3 |

| ТВ            | Testbench                                                              |

| LUT           | Look Up Table                                                          |

| LSDU          | Link Service Data Unit (Data in a frame)                               |

| LPDU          | Link Protocol Data Unit (Data in a frame)                              |

| FF            | Flip Flop                                                              |

| FCS  | Frame Check Sequence also known as CRC   |

|------|------------------------------------------|

| FIFO | First In First Out Buffer                |

| RAM  | Random Access Memory                     |

| RCT  | Redundancy Control Trailer               |

| ROM  | Read Only Memory                         |

| FPGA | Field Programmable Gate Array            |

| VHDL | Hardware description Language for FPGA's |

Table 3: Abbreviations

## 1 Introduction

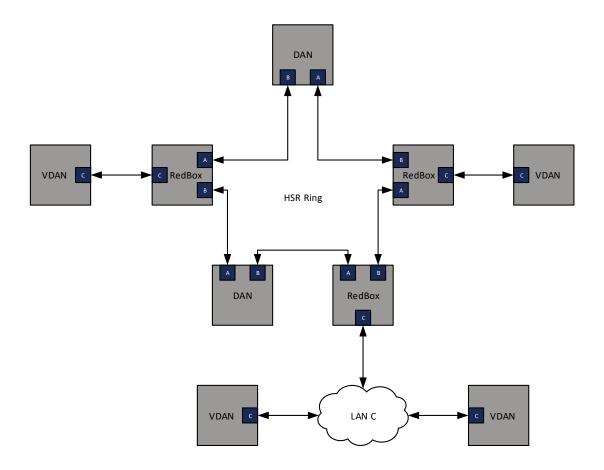

#### 1.1 Context Overview

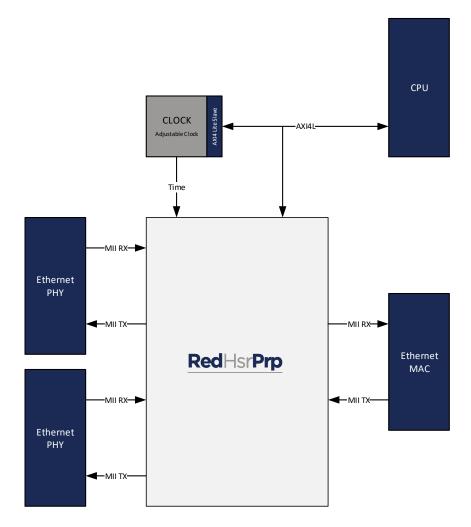

The HSR&PRP Redundancy Core is meant as a co-processing handling network redundancy, intercepts the Media Independent Interface (MII) on the Ethernet path between the MAC and PHY where it handles all redundancy traffic. This means it duplicates and tags frames coming from the Ethernet MAC and does duplicate discarding and untagging on the paths from the Ethernet PHYs. If run in HSR mode it also does the forwarding according to IEC62439.3 between the Ethernet PHYs. It also generates and processes HSR&PRP Supervision frames directly in hardware using the same data path as normal traffic coming from or going to the Ethernet MAC. This also means that it uses a small amount (around 1 frame every 2 seconds per node) of the bandwidth on the MII so if 100% Network traffic shall be constantly sent by the Ethernet MAC it would eventually drop some frames to still handle HSR&PRP. The HSR&PRP Redundancy Core is designed to work in cooperation with the Counter Clock core from NetTimeLogic (not a requirement). It contains an AXI4Lite slave for configuration from a CPU, this is however not required since the HSR&PRP Core can also be configured statically via signals/constants directly from within the FPGA.

The HSR&PRP Core can be combined with a PTP Transparent Clock from NetTime-Logic to handle also time synchronization.

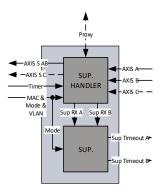

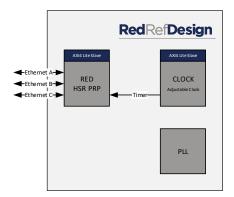

Figure 1: Context Block Diagram

#### 1.2 Function

The HSR&PRP core handles the redundancy according to IEC63439-3. It duplicates and tags frames in the path to the PHYs and discards duplicates and untags frames on the path to the MAC. It optionally contains a Table which contains all nodes connected on the MAC side when run as RedBox. It sends and analyzes HSR/PRP Supervision frames and can do forwarding of frames between the PHY ports if run in HSR mode.

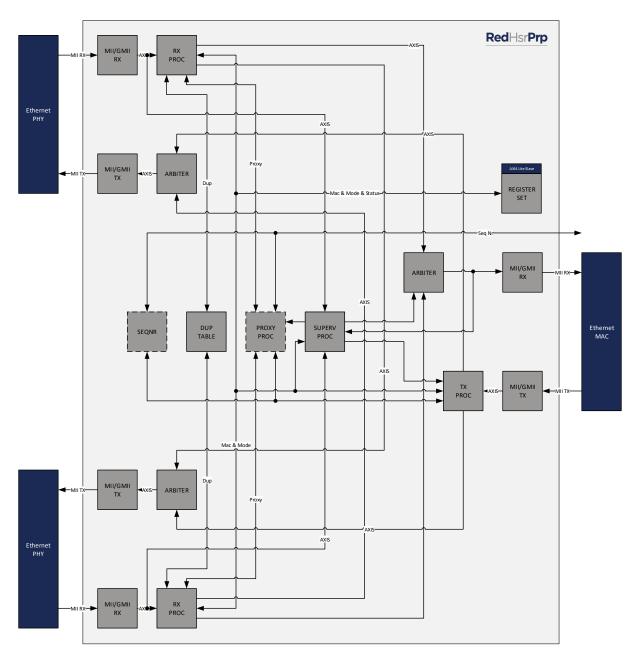

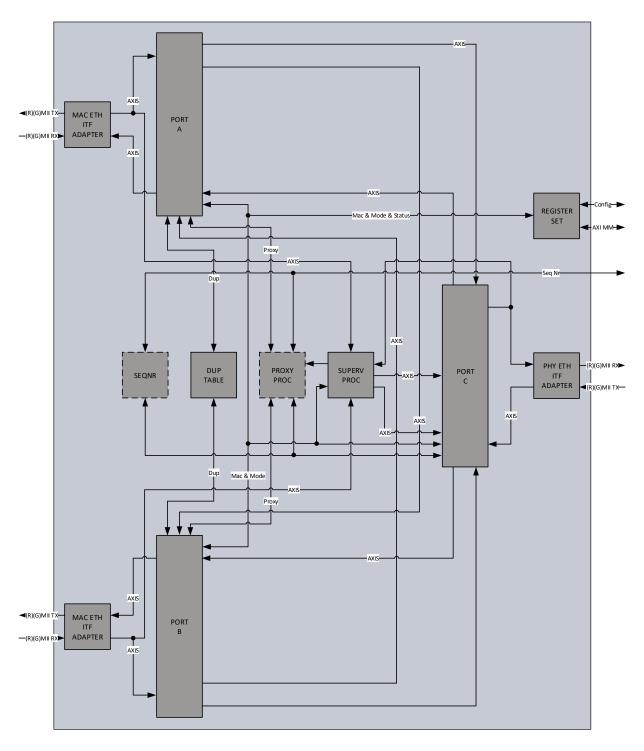

#### 1.3 Architecture

The core is split up into different functional blocks for reduction of the complexity, modularity and maximum reuse of blocks. The interfaces between the functional blocks are kept as small as possible for easier understanding of the core.

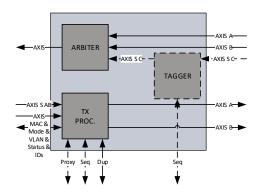

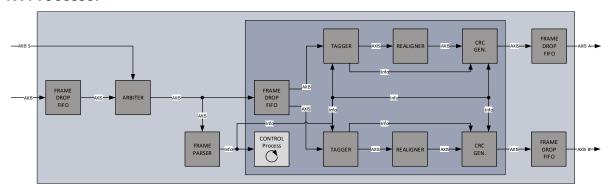

Figure 2: Architecture Block Diagram

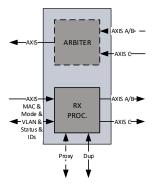

#### **Rx Processor**

This is one of the core modules, it buffers, parses and untags frames as well as taking the forwarding decision whether to forward frames on Ports A/B or Port C. It gets the duplicate decision from the Duplicate Processor and if in RedBox mode also the source Decision from the Proxy Node Processor

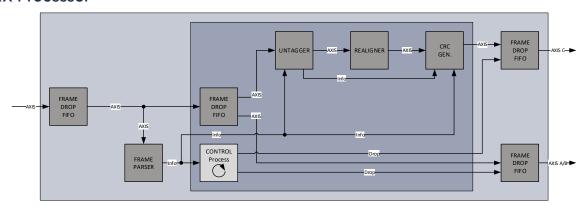

#### **Tx Processor**

This is the other core module, it buffers, parses, tags frames as well as duplicating frames and forwards them to Ports A & B. It gets the sequence number information from the Sequence Number Processor or if in RedBox mode from the Proxy Node Processor.

#### **Supervision Processor**

This block sends Supervision frame for this node and if in RedBox mode also for all nodes in the Proxy Node Table. It also parses the incoming Supervision frames and signals the reception to the Supervision block within which shows the logical link status based on a timer which signals whether supervision frames have been received in the last 5 Supervision frame intervals or not.

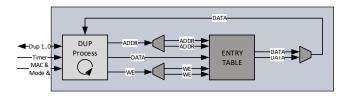

#### **Duplicate Processor**

This block is in charge of detecting duplicates, it contains a Duplication Table which is a pooled Hash Table for each frame received in the redundant Network. Per default it has 2\*\*14 entries, meaning it can handle up to 16k frames in the redundant network. The number of entries is configurable at compile time. Whenever a tagged frame is received it makes an entry in the table for that frame. When the duplicate is received, the entry is cleared. When no duplicate is received within 400ms the entry is aged out.

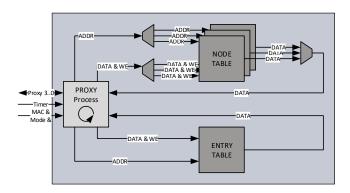

#### **Proxy Node Processor**

This block is only available when run in RedBox mode, it contains entries of all nodes (per default 64, but can be changed at compile time) connected to Port C. It stores the MAC address and a Sequence Number which is used for Supervision frames sending, tagging of frames on sending and in the forward decision when run in HSR mode (frames that are source or destination of a node in the Proxy Node table shall be removed from the ring). Nodes in the table are searched in a linear manner but parallelized to achieve the required speed.

#### **Sequence Number Processor**

This module is only available when not run in RedBox mode, it generates Sequence Number for the tagging.

#### Frame Arbiter

This block multiplexes the frames coming from Ports A & B towards Port C or from Ports A/B &C towards Ports A/B.

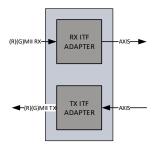

#### (R)(G)MII Receive/Transmit Interface Adapter

These blocks convert the data stream from the (R)(G)MII to a 32bit AXI stream and back form 32bit AXI stream to (R)(G)MII.

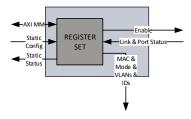

## **Register Set**

This block allows reading status values and writing configuration.

#### 1.4 Deviations from the Standard or Limitations

The deviations and limitations below apply to the core; however, the core is fully compatible with IEC62439-3:

- No Duplicate detection for frames looping in the ring more than once, no strict mode H, can be partly handled by mode X though

- No special SAN handling for PRP, sending always to both ports tagged

- No Supervision counters and Error counters

- No Node Table for Supervision

- PTP Traffic is handled special

- No padding between RCT and CRC for PRP allowed

- No padding of frames when frames are less than 64 bytes after untagging or before tagging

- No IP for core

- Optional cut through frame processing

- No Duplicate Accept mode, only Duplicate Discard

- No wait after reboot

- Allows frame size up to 2044 bytes, but no Jumbo frames (which is according to standard)

- No priority queues

- Only one VLAN supported

- No SNMP support by the core

- No QuadBox support or coupling with other HSR or PRP networks, only PRP/HSR

SAN per default HSR-PRP or HSR-HSR mode can be enabled optionaly

- Frames are sent independent of the physical link status

- No Transparent Reception for PRP

- No Bridging Mode for PRP

- DAN or RedBox own MAC has to be configured, no self-learning

- No Multicast Filter Table

# 2 PRP, HSR and Tail Tagging Basics

# 2.1 Network Redundancy (HSR/PRP) Basics

The two redundancy protocols: Parallel Redundancy Protocol (PRP) and High-availability Seamless Redundancy Protocol (HSR) are closely linked and both standardized in IEC62439-3. The goal of the two Network Redundancy Protocols is to get rid of single point of failures in the network connections, it does not avoid single point of failures in the devices. They use similar principals to achieve redundancy by tagging and untagging frames and duplicating and discarding duplicate frames and mostly differ on the network topology used. The tags contain a Protocol Identifier, a Size Field, a LAN Identifier and most important a Sequence Number to identify frames. Each frame has an individual sequence number per source MAC which is used to do duplicate discarding. They also send periodically so called Supervision frames which allows to supervise the status of the redundant network, e.g. broken links. Each node contains of at least three Ports: The redundant pair Ports A&B and the uplink Port C.

There is also a close coupling to time synchronization according to IEEE1588, which defines a combination of the redundancy with time synchronization in IEC61850-9-3 (Utility Profile). NetTimeLogic's PTP cores can be combined with this core to get a redundant time synchronization solution.

#### 2.1.1 PRP

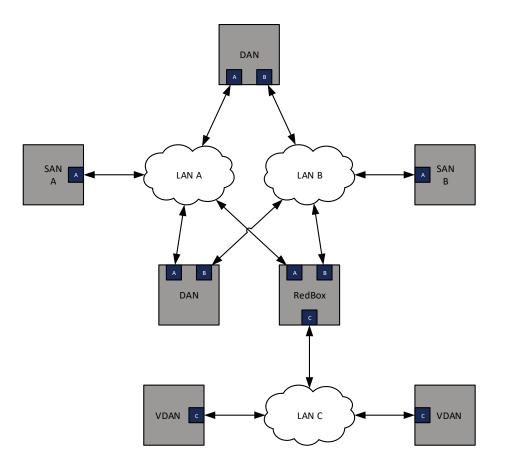

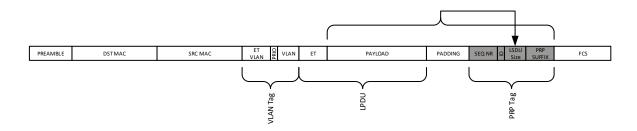

The Parallel Redundancy Protocol (PRP) is defined in chapter 4 of IEC62439-3. The principal is quite simple, it duplicates and tags frames on sending (from Port C to Ports A&B) and does duplicate discarding and untagging on reception (from Ports A&B to Port C). PRP uses two individual networks (LAN A&B) of any topology to achieve redundancy. There is no forwarding between the two networks but the two networks shall have a similar delay. As mentioned frames are tagged on sending, this tag is added at the end of the frame right before the FCS. In case of padding this is inserted between the LPDU and the PRP tag, so the tag is always at the same position in the frame (right before the FCS). Tagging at the end has another advantage, all network nodes in the two individual networks do not have to be PRP aware and just treat the tag as padding. This also means that Single Attached Nodes (SAN) which are only connected to one of the networks can communicate directly with DANs and vice versa ignoring the tags and not creating tags (See 2.1.4, 2.1.5, 2.1.6 and 2.1.7 for details).

A frame is always sent to both networks and the frames are forwarded in the two networks according to switching rules. On reception of a tagged frame for which this node is destination the duplicate discard algorithm is run and only the first frame received forwarded to Port C.

Figure 3: PRP

The frame format of a PRP tagged frame looks as following:

Figure 4: PRP frame

Fields of the PRP tag:

• SEQ NR: 16 bit monotonous increasing (by 1 wrapping through

zero) Sequence Number

• ID: 4bit LAN Identifier, OxA for LAN A, OxB for LAN B

• LSDU Size: 12bit LSDU Size in bytes including payload and PRP

Tag

• PRP Suffix: 16bit PRP Tag Identifier: 0x88FB

WARNING! Frame payload of a non-PRP-tagged frame can always be wrongly detected as a PRP Tag (e.g. Frames from a SAN). This is not critical for the duplication rejection but is critical when untagging, since when the wrongly detected PRP Tag is removed the frame is corrupted because it actually cuts of the last 6 bytes of real payload

See IEC62439-3 chapter 4 for details.

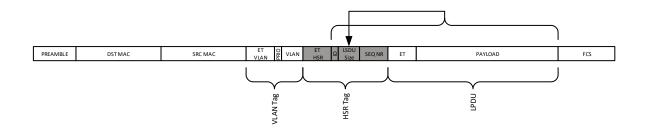

#### 2.1.2 HSR

The High-availability Seamless Redundancy Protocol (HSR) is defined in chapter 5 of IEC62439-3. The principal of HSR is very similar to the one of PRP. It also duplicates and tags frames on sending (from Port C to Ports A&B) and does duplicate discarding and untagging on receiving from Ports A&B to Port C). In contrast to PRP it uses a ring structure for redundancy rather than two individual networks and inserts the tags before the Ethertype of the LPDU rather than appending it at the end of the frame. This means on one hand that there is frame forwarding between the Ports A&B and each node in the redundant network needs to support HSR. There is no scheme to connect Single Attached Nodes (SAN) directly to the ring, they can only be connected via a RedBox to the ring, this can be either a single node or a whole network (See 2.1.4, 2.1.5, 2.1.6 and 2.1.7 for details).

A frame is always sent into both directions of the ring and each node forwards the frame to the next node if it is not destination or source of the frame. If it is the destination (unicast) it removes the frame from the ring and runs the duplicate discard algorithm and forwards the first occurrence of the frame to its Port C. For multicast frames the frame is forwarded on the ring but also the duplicate discard algorithm run towards Port C, the node who injected the frame on the ring is the one that removes the frame from the ring again. There is a special mode called Mode X which does also duplicate rejection on the forwarding path, meaning that only the first occurrence of a frame is forwarded and the duplicate rejected, since it has already passed the ring in both directions. This mode reduces the overall net-

work load since multicast frames do not pass through the whole ring, on the other hand frame discarding gets non-deterministic.

Figure 5: HSR

The frame format of an HSR tagged frame looks as following:

Figure 6: HSR frame

Fields of the HSR tag:

HSR Ethertype: 16bit HSR Tag Identifier: 0x892F

• SEQ NR: 16 bit monotonous increasing (by 1 wrapping through

zero) Sequence Number

• ID: 4bit Path Identifier, 0x0 for Path A, 0x1 for Path B

• LSDU Size: 12bit LSDU Size in bytes including payload and Ethertype

and parts of the HSR Tag

See IEC62439-3 chapter 5 for details.

#### 2.1.3 NO

The NO mode is basically the same like HSR but without tagging and duplicate rejection. So, it duplicates frames on the path from Port C to Port A&B and forwards all frames from Port A&B to Port C (which match the Destination or Multicast). It also forwards frames between the Ports A&B, removing frames on the forwarding where it is Destination or Source.

In this mode no Supervision frames are sent or checked. No tagging or untagging is done.

#### 2.1.4 DAN

A Dual Attached Node (DAN) is an end node participating directly in the redundancy protocols (duplication/duplicate discarding and tagging/untagging). A DAN has only one MAC and sends Supervision frames on behalf of this node only. In case of HSR it removes frames from the ring only for this MAC. Often a DAN is built from a RedBox supporting only one MAC on Port C.

#### 2.1.5 VDAN

A Virtual Dual Attached Node (VDAN) is also an end node with only one MAC, but connected true a RedBox to the redundant network. It does not participate in the redundancy protocols, this is taken care of in the RedBox, so in particular it does no duplication and duplicate discarding or tagging and untagging neither does it send Supervision frames. A VDAN has a single point of failure at the interlink between the RedBox and the node itself.

#### 2.1.6 SAN

A Single Attached Node (SAN) is also an end node which does not participate in the redundancy protocols. So it does neither duplication and duplicate discarding nor tagging and untagging. In case of PRP it can be directly connected to either of the networks (LAN A or B) but only to one at the time. A SAN has a single point of failure since it is connected to only one of the LANs. If a SAN is connected behind a RedBox it is called a VDAN.

#### 2.1.7 RedBox

A Redundancy Box (RedBox) is a network node acting as bridge between the redundant networks and a non-redundant network. It has its own MAC address but it's main task is to act as DANs for the VDANs connected on the non-redundant network. It contains a so called ProxyNodeTable which has entries for each VDAN connected to it. It does duplication of the frames received from Port C towards Port A&B and tags them with an individual monotonous incrementing Sequence Number for each node (MAC) in the ProxyNodeTable. It also creates Supervision frames for each node in the ProxyNodeTable, marking the frames that they were sent via a RedBox. On reception, it does run the duplicate discard algorithm and untagging for all frames, not only the one it is destination. In case of HSR it removes the frames, which are addressed to or sourced by a node in the ProxyNodeTable from the ring acting like multiple DANs in a single device. In addition to this functionality, a RedBox acts as DAN for frames sourced by or addressed to the MAC of the RedBox itself.

# 2.1.8 Supervision

Both protocols define so called Supervision frames (with basically the same format) which have a reserved multicast destination MAC range (01:15:4E:00:01:XX) and Ethertype (0x88FB). These frames are sent periodically which allows other nodes, and the node itself to supervise the status of the redundant network. If not both of the Supervision frames are received from a node, a logical or physical link is broken. In case of HSR the node can supervise its own status by checking if it receives back the supervision frames sent by itself. In case of PRP the Supervision frames also identify DANs from SANs which is needed for untagging frames.

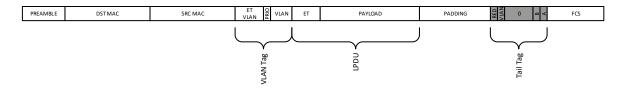

## 2.2 Tail Tagging Basics

Tail Tagging is used to know from which Port (A or B) the frame was received and if it was redundancy tagged when forwarded to Port C and to define when a frame is sent to Port C on which Port (A and/or B) shall be sent (bitmask: only A, only B or both) and if the frame shall be redundancy and/or VLAN tagged or not.

Tail Tagging is often used by switches for e.g. LLDP frames (for e.g. RSTP).

The Tail Tag is a single Byte which is inserted right before the FCS, which means it is part of the payload and the FCS is generated over the Tail Tag.

The Tail Tag will be removed before the frame is forwarded to Ports A & B and it is added before the frame is forwarded to Port C.

The format of the Tail Tag is as following:

Figure 7: Tail Tagged frame

Fields of the Tail tag:

| • | RED: | Bit 7, indicating | if the frame | was redunda    | ancy tagged    | on |

|---|------|-------------------|--------------|----------------|----------------|----|

|   |      | reception (from   | Port A & B)  | or if the fran | ne shall be re | e- |

dundancy tagged on transmission (to Port A & B)

• VLAN: Bit 6, indicating if the frame was VLAN tagged on

reception (from Port A & B) or if the frame shall be VLAN tagged on transmission, if VLAN tagging is enabled (to

Port A & B)

• Port B: Bit 1, indicating if the frame is coming from Port B on

reception or if the frame shall be sent to Port B on

transmission

• Port A: Bit 0, indicating if the frame is coming from Port A on

reception or if the frame shall be sent to Port A on

transmission

WARNING! When Tail Tagging is enabled every frame going to Port C, has to be Tail Tagged, otherwise the last byte before the FCS will be treated as Tail Tag which will result in an undefined behavior.

# **3** Register Set

This is the register set of the HSR&PRP Core. It is accessible via AXI4Lite Memory Mapped. All registers are 32bit wide, no burst access, no unaligned access, no byte enables, no timeouts are supported. Register address space is not contiguous. Register addresses are only offsets in the memory area where the core is mapped in the AXI interconnects. Non existing register access in the mapped memory area is answered with a slave decoding error.

# 3.1 Register Overview

| Registerset Overview            |                                                       |            |        |  |

|---------------------------------|-------------------------------------------------------|------------|--------|--|

| Name                            | Description                                           | Offset     | Access |  |

| Red HsrPrpControl Reg           | HsrPrp Enable Control Register                        | 0x0000000  | RW     |  |

| Red HsrPrpStatus Reg            | HsrPrp Error Status Register                          | 0x0000004  | WC     |  |

| Red HsrPrpVersion Reg           | HsrPrp Version Register                               | 0x000000C  | RO     |  |

| Red HsrPrpFrameCountControl Reg | HsrPrp Status Control Register                        | 0x0000010  | RW     |  |

| Red HsrPrpRxFrameCountA Reg     | HsrPrp Received Frames Count Port A Register          | 0x00000020 | RO     |  |

| Red HsrPrpRxErrCountA Reg       | HsrPrp Received Error Frames Count Port A Register    | 0x00000024 | RO     |  |

| Red HsrPrpTxFrameCountA Reg     | HsrPrp Transmitted Frames Count Port A Register       | 0x00000030 | RO     |  |

| Red HsrPrpTxErrCountA Reg       | HsrPrp Transmitted Error Frames Count Port A Register | 0x00000034 | RO     |  |

| Red HsrPrpRxFrameCountB Reg     | HsrPrp Received Frames Count Port B Register          | 0x00000040 | RO     |  |

| Red HsrPrpRxErrCountB Reg       | HsrPrp Received Error Frames Count Port B Register    | 0x00000044 | RO     |  |

| Red HsrPrpTxFrameCountB Reg     | HsrPrp Transmitted Frames Count Port B Register       | 0x0000050  | RO     |  |

| Red HsrPrpTxErrCountB Reg       | HsrPrp Transmitted Error Frames Count Port B Register | 0x00000054 | RO     |  |

| Red HsrPrpRxFrameCountC Reg     | HsrPrp Received Frames Count Port C Register          | 0x00000060 | RO     |  |

| Red HsrPrpRxErrCountC Reg       | HsrPrp Received Error Frames Count Port C Register    | 0x00000064 | RO     |  |

| Red HsrPrpTxFrameCountC Reg | HsrPrp Transmitted Frames Count Port C Register       | 0x0000070  | RO |

|-----------------------------|-------------------------------------------------------|------------|----|

| Red HsrPrpTxErrCountC Reg   | HsrPrp Transmitted Error Frames Count Port C Register | 0x00000074 | RO |

| Red HsrPrpConfigControl Reg | HsrPrp Configuration Control Register                 | 0x0000080  | RW |

| Red HsrPrpConfigMode Reg    | HsrPrp Configuration Mode Register                    | 0x00000084 | RW |

| Red HsrPrpConfigVlan Reg    | HsrPrp Configuration VLAN Register                    | 0x00000088 | RW |

| Red HsrPrpMacControl Reg    | HsrPrp MAC Control Register                           | 0x00000100 | RW |

| Red HsrPrpMac1 Reg          | HsrPrp MAC 0-3                                        | 0x00000104 | RW |

| Red HsrPrpMac2 Reg          | HsrPrp MAC 4-5                                        | 0x00000108 | RW |

Table 4: Register Set Overview

# **3.2 Register Descriptions**

## 3.2.1 General

# 3.2.1.1 RED HsrPrp Control Register

Used for general control over the HSR&PRP Core, all configurations on the core shall only be done when disabled.

| RED HsrPrpControl Reg                                                               |        |

|-------------------------------------------------------------------------------------|--------|

| Reg Description                                                                     |        |

| 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 | 0      |

|                                                                                     |        |

|                                                                                     |        |

|                                                                                     | Ш      |

|                                                                                     | BLE    |

|                                                                                     | ENABLI |

|                                                                                     | Ш      |

|                                                                                     |        |

|                                                                                     |        |

| RO                                                                                  | RW     |

|                                                                                     |        |

| Reset: 0x0000000                                                                    |        |

| Offset: 0x0000                                                                      |        |

| Name   | Description      | Bits     | Access |

|--------|------------------|----------|--------|

| -      | Reserved, read 0 | Bit:31:1 | RO     |

| ENABLE | Enable           | Bit: 0   | RW     |

RedHsrPrp Reference Manual 2.5 Page 24 of 98

# 3.2.1.2 RED HsrPrp Status Register

Shows the current status of the RED HsrPrp core, status bits of supervision timeouts.

| RED HsrPrpStatus Reg                                        |      |        |        |        |   |   |    |   |   |   |           |           |

|-------------------------------------------------------------|------|--------|--------|--------|---|---|----|---|---|---|-----------|-----------|

| Reg Description                                             |      |        |        |        |   |   |    |   |   |   |           |           |

| 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 | 2 11 | 10     | 9      | 8      | 7 | 6 | 5  | 4 | 3 | 2 | 1         | 0         |

|                                                             |      | LINK_C | LINK_B | LINK_A |   |   |    | 1 |   |   | TIMEOUT_B | TIMEOUT_A |

| RO                                                          |      | RO     | RO     | RO     |   |   | RO | Э |   |   | WC.       | WC        |

| Reset: 0x0000000                                            | •    |        |        |        | • |   |    |   |   | • |           |           |

| Offset: 0x0004                                              |      |        |        |        |   |   |    |   |   |   |           |           |

| Name      | Description                                                                           | Bits      | Access |

|-----------|---------------------------------------------------------------------------------------|-----------|--------|

| -         | Reserved, read 0                                                                      | Bit:31:11 | RO     |

| LINK_C    | Link state of Port C                                                                  | Bit: 10   | RO     |

| LINK_B    | Link state of Port B                                                                  | Bit: 9    | RO     |

| LINK_A    | Link state of Port A                                                                  | Bit: 8    | RO     |

| -         | Reserved, read 0                                                                      | Bit:7:2   | RO     |

| TIMEOUT_B | No Supervision frames were received on B for the defined number supervision intervals | Bit: 1    | WC     |

| TIMEOUT_A | No Supervision frames were received on A for the defined number supervision intervals | Bit: 0    | WC     |

RedHsrPrp Reference Manual 2.5 Page 25 of 98

RedHsrPrp Reference Manual 2.5 Page 26 of 98

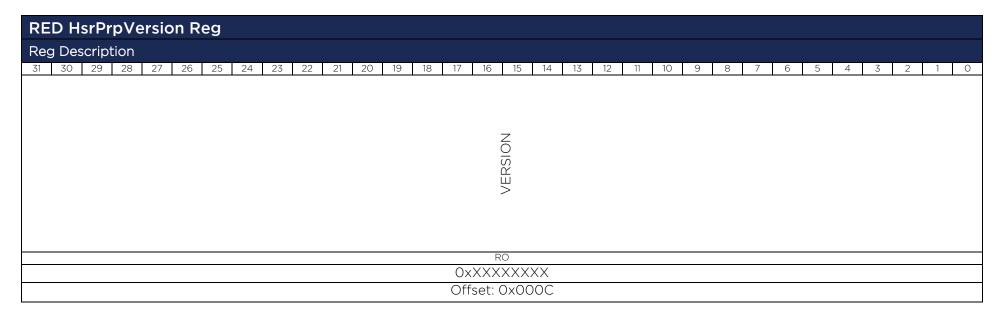

## 3.2.1.3 RED HsrPrp Version Register

Version of the IP core, even though is seen as a 32bit value, bits 31 down to 24 represent the major, bits 23 down to 16 the minor and bits 15 down to 0 the build numbers.

| Name    | Description         | Bits      | Access |

|---------|---------------------|-----------|--------|

| VERSION | Version of the core | Bit: 31:0 | RO     |

RedHsrPrp Reference Manual 2.5 Page 27 of 98

# 3.2.1.4 RED HsrPrp Frame Count Control Register

Used for clearing all statistic counters

Only available if the generic PortStatusSupport\_Gen is true.

| RE  | DΗ  | srPi  | рFr  | ame | eCo | unt | Con | trol | Re | g  |    |    |    |     |        |        |       |     |    |    |    |   |   |   |   |   |   |   |   |   |          |

|-----|-----|-------|------|-----|-----|-----|-----|------|----|----|----|----|----|-----|--------|--------|-------|-----|----|----|----|---|---|---|---|---|---|---|---|---|----------|

| Reg | Des | scrip | tion |     |     |     |     |      |    |    |    |    |    |     |        |        |       |     |    |    |    |   |   |   |   |   |   |   |   |   |          |

| 31  | 30  | 29    | 28   | 27  | 26  | 25  | 24  | 23   | 22 | 21 | 20 | 19 | 18 | 17  | 16     | 15     | 14    | 13  | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0        |

|     |     |       |      |     |     |     |     |      |    |    |    |    |    |     |        |        |       |     |    |    |    |   |   |   |   |   |   |   |   |   |          |

|     |     |       |      |     |     |     |     |      |    |    |    |    |    |     |        |        |       |     |    |    |    |   |   |   |   |   |   |   |   |   |          |

|     |     |       |      |     |     |     |     |      |    |    |    |    |    |     |        |        |       |     |    |    |    |   |   |   |   |   |   |   |   |   |          |

|     |     |       |      |     |     |     |     |      |    |    |    |    |    |     |        |        |       |     |    |    |    |   |   |   |   |   |   |   |   |   | $\simeq$ |

|     |     |       |      |     |     |     |     |      |    |    |    |    |    |     |        | 1      |       |     |    |    |    |   |   |   |   |   |   |   |   |   | EAI      |

|     |     |       |      |     |     |     |     |      |    |    |    |    |    |     |        |        |       |     |    |    |    |   |   |   |   |   |   |   |   |   | CLE      |

|     |     |       |      |     |     |     |     |      |    |    |    |    |    |     |        |        |       |     |    |    |    |   |   |   |   |   |   |   |   |   |          |

|     |     |       |      |     |     |     |     |      |    |    |    |    |    |     |        |        |       |     |    |    |    |   |   |   |   |   |   |   |   |   |          |

|     |     |       |      |     |     |     |     |      |    |    |    |    |    |     |        |        |       |     |    |    |    |   |   |   |   |   |   |   |   |   |          |

|     |     |       |      |     |     |     |     |      |    |    |    |    |    |     |        |        |       |     |    |    |    |   |   |   |   |   |   |   |   |   |          |

|     |     |       |      |     |     |     |     |      |    |    |    |    |    |     | R      | 0      |       |     |    |    |    |   |   |   |   |   |   |   |   |   | RW       |

|     |     |       |      |     |     |     |     |      |    |    |    |    |    | Res | set: C | x000   | 0000  | 000 |    |    |    |   |   |   |   |   |   |   |   |   |          |

|     |     |       |      |     |     |     |     |      |    |    |    |    |    | (   | Offse  | et: Ox | 0010  | )   |    |    |    |   |   |   |   |   |   |   |   |   |          |

|     |     |       |      |     |     |     |     |      |    |    |    |    |    | (   | Offse  | et: Ox | :0010 | )   |    |    |    |   |   |   |   |   |   |   |   |   |          |

| Name  | Description                       | Bits     | Access |

|-------|-----------------------------------|----------|--------|

| -     | Reserved, read 0                  | Bit:31:1 | RO     |

| CLEAR | Clear all counters (self cleared) | Bit: 0   | RW     |

## 3.2.1.5 RED HsrPrp RX Frame Count Registers

Received number of frames on the specific Port [X]: X= A, B, C. Offsets: Port A: 0x0020, Port B: 0x0040, Port C: 0x0060. Includes also erroneous frames.

Only available if the generic PortStatusSupport\_Gen is true.

| Re  | d H   | srPr  | pRx  | Fra | meC | our | nt[X] | ] Re | g  |    |    |     |        |      |      |            |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|-----|-------|-------|------|-----|-----|-----|-------|------|----|----|----|-----|--------|------|------|------------|------|------|-----|----|----|---|---|---|---|---|---|---|---|---|---|

| Reg | g Des | scrip | tion |     |     |     |       |      |    |    |    |     |        |      |      |            |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

| 31  | 30    | 29    | 28   | 27  | 26  | 25  | 24    | 23   | 22 | 21 | 20 | 19  | 18     | 17   | 16   | 15         | 14   | 13   | 12  | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|     |       |       |      |     |     |     |       |      |    |    |    |     |        |      |      |            |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|     |       |       |      |     |     |     |       |      |    |    |    |     |        |      |      |            |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|     |       |       |      |     |     |     |       |      |    |    |    |     |        |      |      | <i>,</i> 0 |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|     |       |       |      |     |     |     |       |      |    |    |    |     |        |      |      | Ш          |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|     |       |       |      |     |     |     |       |      |    |    |    |     |        |      |      | AMES       |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|     |       |       |      |     |     |     |       |      |    |    |    |     |        |      |      | FR/        |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|     |       |       |      |     |     |     |       |      |    |    |    |     |        |      |      |            |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|     |       |       |      |     |     |     |       |      |    |    |    |     |        |      |      | X.         |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|     |       |       |      |     |     |     |       |      |    |    |    |     |        |      |      |            |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|     |       |       |      |     |     |     |       |      |    |    |    |     |        |      |      |            |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|     |       |       |      |     |     |     |       |      |    |    |    |     |        |      |      |            |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|     |       |       |      |     |     |     |       |      |    |    |    |     |        |      |      | 20         |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|     |       |       |      |     |     |     |       |      |    |    |    |     |        |      |      | 0000       |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|     |       |       |      |     |     |     |       |      |    |    |    | Off | set: ( | 00xC | 020, | 0x00       | )40, | 0x0( | 060 |    |    |   |   |   |   |   |   |   |   |   |   |

| Name      | Description                                   | Bits      | Access |

|-----------|-----------------------------------------------|-----------|--------|

| RX_FRAMES | Received number of frames on Port [X] X=A,B,C | Bit: 31:0 | RO     |

## 3.2.1.6 RED HsrPrp RX Error Count Registers

Received number of erroneous frames on the specific Port [X]: X= A, B, C. Offsets: Port A: 0x0024, Port B: 0x0044, Port C: 0x0064. Only available if the generic PortStatusSupport\_Gen is true.

| Red | d H | srPr  | pRx  | Err | Cou | nt[X | [] Re | eg |    |    |    |     |      |      |      |      |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|-----|-----|-------|------|-----|-----|------|-------|----|----|----|----|-----|------|------|------|------|------|------|-----|----|----|---|---|---|---|---|---|---|---|---|---|

| Reg | Des | scrip | tion |     |     |      |       |    |    |    |    |     |      |      |      |      |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

| 31  | 30  | 29    | 28   | 27  | 26  | 25   | 24    | 23 | 22 | 21 | 20 | 19  | 18   | 17   | 16   | 15   | 14   | 13   | 12  | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|     |     |       |      |     |     |      |       |    |    |    |    |     |      |      |      |      |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|     |     |       |      |     |     |      |       |    |    |    |    |     |      |      |      |      |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|     |     |       |      |     |     |      |       |    |    |    |    |     |      |      |      | Ϋ́,  |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|     |     |       |      |     |     |      |       |    |    |    |    |     |      |      |      | ERR  |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|     |     |       |      |     |     |      |       |    |    |    |    |     |      |      |      | X'   |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|     |     |       |      |     |     |      |       |    |    |    |    |     |      |      |      |      |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|     |     |       |      |     |     |      |       |    |    |    |    |     |      |      |      |      |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|     |     |       |      |     |     |      |       |    |    |    |    |     |      |      |      |      |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|     |     |       |      |     |     |      |       |    |    |    |    |     |      |      |      | RO   |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|     |     |       |      |     |     |      |       |    |    |    |    |     |      | Ox   | (00C | 000  | 00   |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|     |     |       |      |     |     |      |       |    |    |    |    | Off | set: | )0xC | )24, | 0x00 | )44, | 0x0( | 064 |    |    |   |   |   |   |   |   |   |   |   |   |

| Na | ame   | Description                                             | Bits      | Access |

|----|-------|---------------------------------------------------------|-----------|--------|

| R  | X_ERR | Received number of erroneous frames on Port [X] X=A,B,C | Bit: 31:0 | RO     |

RedHsrPrp Reference Manual 2.5 Page 30 of 98

## 3.2.1.7 RED HsrPrp TX Frame Count Registers

Transmitted number of frames on the specific Port [X]: X= A, B, C. Offsets: Port A: 0x0030, Port B: 0x0050, Port C: 0x0070. Includes also erroneous frames.

Only available if the generic PortStatusSupport\_Gen is true.

| Re | d H   | srPr  | рТх  | Frai | meC | oun | t[X] | ] Re | g  |    |    |     |      |      |      |          |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|----|-------|-------|------|------|-----|-----|------|------|----|----|----|-----|------|------|------|----------|------|------|-----|----|----|---|---|---|---|---|---|---|---|---|---|

| Re | g Des | scrip | tion |      |     |     |      |      |    |    |    |     |      |      |      |          |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

| 31 | 30    | 29    | 28   | 27   | 26  | 25  | 24   | 23   | 22 | 21 | 20 | 19  | 18   | 17   | 16   | 15       | 14   | 13   | 12  | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|    |       |       |      |      |     |     |      |      |    |    |    |     |      |      |      |          |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|    |       |       |      |      |     |     |      |      |    |    |    |     |      |      |      |          |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|    |       |       |      |      |     |     |      |      |    |    |    |     |      |      |      |          |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|    |       |       |      |      |     |     |      |      |    |    |    |     |      |      |      | Ш        |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|    |       |       |      |      |     |     |      |      |    |    |    |     |      |      |      | AMES     |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|    |       |       |      |      |     |     |      |      |    |    |    |     |      |      |      | F.R.     |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|    |       |       |      |      |     |     |      |      |    |    |    |     |      |      |      |          |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|    |       |       |      |      |     |     |      |      |    |    |    |     |      |      |      | $\simeq$ |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|    |       |       |      |      |     |     |      |      |    |    |    |     |      |      |      |          |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|    |       |       |      |      |     |     |      |      |    |    |    |     |      |      |      |          |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|    |       |       |      |      |     |     |      |      |    |    |    |     |      |      |      |          |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|    |       |       |      |      |     |     |      |      |    |    |    |     |      |      |      | RO       |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|    |       |       |      |      |     |     |      |      |    |    |    |     |      |      |      | 0000     |      |      |     |    |    |   |   |   |   |   |   |   |   |   |   |

|    |       |       |      |      |     |     |      |      |    |    |    | Off | set: | 0x0( | 030, | 0x00     | 050, | 0x0( | 270 |    |    |   |   |   |   |   |   |   |   |   |   |

| Name      | Description                                      | Bits      | Access |

|-----------|--------------------------------------------------|-----------|--------|

| RX_FRAMES | Transmitted number of frames on Port [X] X=A,B,C | Bit: 31:0 | RO     |

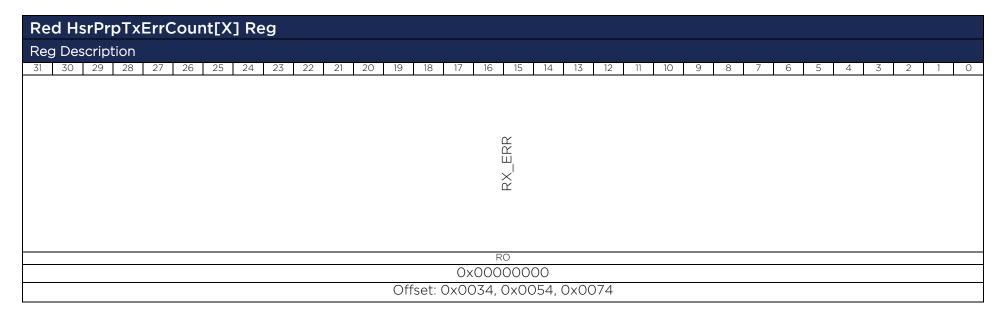

## 3.2.1.8 RED HsrPrp TX Error Count Registers

Transmitted number of erroneous frames on the specific Port [X]: X= A, B, C. Offsets: Port A: 0x0034, Port B: 0x0054, Port C: 0x0074.

Only available if the generic PortStatusSupport\_Gen is true.

| Name   | Description                                                | Bits      | Access |

|--------|------------------------------------------------------------|-----------|--------|

| RX_ERR | Transmitted number of erroneous frames on Port [X] X=A,B,C | Bit: 31:0 | RO     |

RedHsrPrp Reference Manual 2.5 Page 32 of 98

# 3.2.1.9 RED HsrPrp Config Control Register

Configuration valid bits, used to mark the corresponding fields as valid.

| RED HsrPrpConfigControl Reg                                                     |   |          |          |  |  |  |  |  |

|---------------------------------------------------------------------------------|---|----------|----------|--|--|--|--|--|

| Reg Description                                                                 |   |          |          |  |  |  |  |  |

| 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 | 2 | 1        | 0        |  |  |  |  |  |

|                                                                                 |   | VLAN_VAL | MODE_VAL |  |  |  |  |  |

| RO                                                                              |   | RW       | RW       |  |  |  |  |  |

| Reset: 0x0000000                                                                |   |          |          |  |  |  |  |  |

| Offset: 0x0080                                                                  |   |          |          |  |  |  |  |  |

| Name     | Description              | Bits     | Access |

|----------|--------------------------|----------|--------|

| -        | Reserved, read 0         | Bit:31:2 | RO     |

| VLAN_VAL | VLAN valid (autocleared) | Bit: 1   | RW     |

| MODE_VAL | Mode valid (autocleared) | Bit: 0   | RW     |

## 3.2.1.10 RED HsrPrp Config Mode Register

Mode to run the core in, Either HSR, PRP or NON. All other modes all traffic is dropped. If Promiscuous mode is enabled all traffic will be forwarded to Port C, duplicates rejected but all destinations. If no-forwarding is enabled frames will not be forwarded between Ports A & B. If tail-tagging is enabled each frame going to Port C needs to have a tail-tag, each frame coming from Port C will have a tail-tag containing the source port and if the frame was redundancy tagged or not. If PRP untagging is enabled, PRP tagged frames will be untagged, this shall only be enabled if it can be guaranteed that all frames in the redundant network contain a PRP tag, otherwise the frame might get corrupted if the payload matches the PRP trailer pattern which will then be removed (frame shortened by 6 bytes which was actual payload)

| RED HsrPrpConfigMode Reg         |             |               |              |            |             |    |    |    |    |    |    |        |   |   |   |    |   |   |   |      |   |

|----------------------------------|-------------|---------------|--------------|------------|-------------|----|----|----|----|----|----|--------|---|---|---|----|---|---|---|------|---|

| Reg Description                  |             |               |              |            |             |    |    |    |    |    |    |        |   |   |   |    |   |   |   |      |   |

| 31 30 29 28 27 26 25 24 23 22 21 | 20          | 19            | 18           | 17         | 16          | 15 | 14 | 13 | 12 | 11 | 10 | 9      | 8 | 7 | 6 | 5  | 4 | 3 | 2 | 1    | 0 |

| 1                                | CUT_THROUGH | PRP_UNTAGGING | TAIL_TAGGING | NO_FORWARD | PROMISCUOUS |    |    |    |    | 1  |    | NET_ID |   |   |   | ı  |   |   |   | MODE |   |

| RO                               | RW          | RW            | RW           | RW         | RW          |    | RV | V  |    | RO |    | RW     |   |   |   | RO |   |   |   | RW   |   |

| Reset: 0x0000000                 |             |               |              |            |             |    |    |    |    |    |    |        |   |   |   |    |   |   |   |      |   |

| Offset: 0x0084                   |             |               |              |            |             |    |    |    |    |    |    | •      |   |   |   |    |   |   |   |      |   |

| Name          | Description                                                                                                                                                                                                    | Bits      | Access |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------|

| -             | Reserved, read 0                                                                                                                                                                                               | Bit:31:21 | RO     |

| CUT_THROUIGH  | Enable cut through frame processing                                                                                                                                                                            | Bit:20    | RW     |

| PRP_UNTAGGING | Enables untagging for PRP tagged frames, only set if sure that the incoming frames always have a PRP tag (otherwise payload might be intrepreted as PRP tag which will end in a corrupt frame (6bytes cut off) | Bit:19    | RW     |

| TAIL_TAGGING  | Enables Tail Tagging, all Frames coming to Port C shall be tail tagged, all Frames comming from Port C will contain a tail tag                                                                                 | Bit:18    | RW     |

| NO_FORWARD    | Disables forwarding between Port A&B                                                                                                                                                                           | Bit:17    | RW     |

| PROMISCUOUS   | Promiscuous Mode                                                                                                                                                                                               | Bit:16    | RW     |

| REDBOX_ID     | RedBox identifier, used for HSR-PRP mode (0xA or 0xB)                                                                                                                                                          | Bit:15:12 | RW     |

| -             | Reserved, read 0                                                                                                                                                                                               | Bit:11    | RO     |

| NET_ID        | Network identifier, used for HSR-PRP mode                                                                                                                                                                      | Bit:10:8  | RW     |

| -             | Reserved, read 0                                                                                                                                                                                               | Bit:7:3   | RO     |

| MODE          | Profile (0 Non, 1 PRP, 2 HSR, 5 HSR-PRP, 6 HSR-HSR)                                                                                                                                                            | Bit:2:0   | RW     |

RedHsrPrp Reference Manual 2.5 Page 35 of 98

# 3.2.1.11RED HsrPrp Config Vlan Register

VLAN for 802.3q priority tagging or virtual networks. VLAN can be enabled or disabled.

| RED HsrPrpConfigVlan Reg                     |                                          |  |  |  |  |  |  |  |  |

|----------------------------------------------|------------------------------------------|--|--|--|--|--|--|--|--|

| Reg Description                              |                                          |  |  |  |  |  |  |  |  |

| 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 | 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |  |  |  |  |  |  |  |  |

|                                              | VLAN KLAN                                |  |  |  |  |  |  |  |  |

| RO                                           | RW RW                                    |  |  |  |  |  |  |  |  |

| Reset: 0x0000000                             |                                          |  |  |  |  |  |  |  |  |

| Offset: 0x0088                               |                                          |  |  |  |  |  |  |  |  |

| Name    | Description                         | Bits      | Access |

|---------|-------------------------------------|-----------|--------|

| -       | Reserved, read 0                    | Bit:31:17 | RO     |

| VLAN_EN | VLAN enable (0 disabled, 1 enabled) | Bit: 16   | RW     |

| VLAN    | VLAN                                | Bit: 15:0 | RW     |

## 3.2.2 Mac

## 3.2.2.1 RED HsrPrp Mac Control Register

Configuration valid bits, used to mark the corresponding fields as valid.

| RE  | RED HsrPrpMacControl Reg |    |    |    |    |    |    |       |    |    |    |    |    |    |       |       |      |    |    |    |    |   |   |   |   |   |   |   |   |   |    |

|-----|--------------------------|----|----|----|----|----|----|-------|----|----|----|----|----|----|-------|-------|------|----|----|----|----|---|---|---|---|---|---|---|---|---|----|

| Reg | Reg Description          |    |    |    |    |    |    |       |    |    |    |    |    |    |       |       |      |    |    |    |    |   |   |   |   |   |   |   |   |   |    |

| 31  | 30                       | 29 | 28 | 27 | 26 | 25 | 24 | 23    | 22 | 21 | 20 | 19 | 18 | 17 | 16    | 15    | 14   | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0  |

|     |                          |    |    |    |    |    |    |       |    |    |    |    |    |    |       |       |      |    |    |    |    |   |   |   |   |   |   |   |   |   |    |

|     |                          |    |    |    |    |    |    |       |    |    |    |    |    |    |       |       |      |    |    |    |    |   |   |   |   |   |   |   |   |   |    |

|     |                          |    |    |    |    |    |    |       |    |    |    |    |    |    |       |       |      |    |    |    |    |   |   |   |   |   |   |   |   |   |    |

|     |                          |    |    |    |    |    |    |       |    |    |    |    |    |    |       |       |      |    |    |    |    |   |   |   |   |   |   |   |   |   | Ĭ  |

|     |                          |    |    |    |    |    |    |       |    |    |    |    |    |    |       | ı     |      |    |    |    |    |   |   |   |   |   |   |   |   |   | >  |

|     |                          |    |    |    |    |    |    |       |    |    |    |    |    |    |       |       |      |    |    |    |    |   |   |   |   |   |   |   |   |   | AC |

|     |                          |    |    |    |    |    |    |       |    |    |    |    |    |    |       |       |      |    |    |    |    |   |   |   |   |   |   |   |   |   | Σ  |

|     |                          |    |    |    |    |    |    |       |    |    |    |    |    |    |       |       |      |    |    |    |    |   |   |   |   |   |   |   |   |   |    |

|     |                          |    |    |    |    |    |    |       |    |    |    |    |    |    |       |       |      |    |    |    |    |   |   |   |   |   |   |   |   |   |    |

|     | RO RW                    |    |    |    |    |    |    |       |    |    |    |    |    |    |       |       |      |    |    |    |    |   |   |   |   |   |   |   |   |   |    |

|     |                          |    |    |    |    |    |    | IT VV |    |    |    |    |    |    |       |       |      |    |    |    |    |   |   |   |   |   |   |   |   |   |    |

|     | Reset: 0x0000000         |    |    |    |    |    |    |       |    |    |    |    |    |    |       |       |      |    |    |    |    |   |   |   |   |   |   |   |   |   |    |

|     |                          |    |    |    |    |    |    |       |    |    |    |    |    | (  | Offse | t: Ox | 0100 | )  |    |    |    |   |   |   |   |   |   |   |   |   |    |

| Name    | Description                      | Bits     | Access |

|---------|----------------------------------|----------|--------|

| -       | Reserved, read 0                 | Bit:31:1 | RO     |

| MAC_VAL | MAC address valid (selfclearing) | Bit: 0   | RW     |

RedHsrPrp Reference Manual 2.5 Page 37 of 98

## 3.2.2.2RED HsrPrp MAC 1 Register

MAC address of the node. LSB is transferred first on the network.

E.g. 0x01234567 => MAC: 67:45:32:01:XX:XX.

| RED HsrPrpMac1 Reg      | RED HsrPrpMac1 Reg      |                       |                 |  |  |  |  |  |  |  |  |

|-------------------------|-------------------------|-----------------------|-----------------|--|--|--|--|--|--|--|--|

| Reg Description         |                         |                       |                 |  |  |  |  |  |  |  |  |

| 31 30 29 28 27 26 25 24 | 23 22 21 20 19 18 17 16 | 15 14 13 12 11 10 9 8 | 7 6 5 4 3 2 1 0 |  |  |  |  |  |  |  |  |

| MAC(3)                  | MAC(2)                  | MAC(1)                | MAC(0)          |  |  |  |  |  |  |  |  |

| RW RW RW                |                         |                       |                 |  |  |  |  |  |  |  |  |

| Reset: 0x0000000        |                         |                       |                 |  |  |  |  |  |  |  |  |

|                         | Offset: 0x0104          |                       |                 |  |  |  |  |  |  |  |  |

| Name   | Description | Bits      | Access |

|--------|-------------|-----------|--------|

| MAC(3) | MAC Byte 3  | Bit:31:24 | RW     |

| MAC(2) | MAC Byte 2  | Bit:23:16 | RW     |

| MAC(1) | MAC Byte 1  | Bit:15:8  | RW     |

| MAC(0) | MAC Byte 0  | Bit:7:0   | RW     |

RedHsrPrp Reference Manual 2.5

## 3.2.2.3RED HsrPrp MAC 2 Register

MAC address of the node. LSB is transferred first on the network.

E.g. 0x0004567 => MAC: XX:XX:XX:67:45.

| RED HsrPrpMac2 Reg                           |                          |                 |  |  |  |  |  |  |

|----------------------------------------------|--------------------------|-----------------|--|--|--|--|--|--|

| Reg Description                              |                          |                 |  |  |  |  |  |  |

| 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 | 16 15 14 13 12 11 10 9 8 | 7 6 5 4 3 2 1 0 |  |  |  |  |  |  |

| 1                                            | MAC(5)                   | MAC(4)          |  |  |  |  |  |  |

| RO                                           | RW                       | RW              |  |  |  |  |  |  |

|                                              | Reset: 0x0000000         |                 |  |  |  |  |  |  |

| C                                            | fset: 0x0108             | ·               |  |  |  |  |  |  |

| Name   | Description      | Bits      | Access |

|--------|------------------|-----------|--------|

| -      | Reserved, read 0 | Bit:31:16 | RO     |

| MAC(5) | MAC Byte 5       | Bit:15:8  | RW     |

| MAC(4) | MAC Byte 4       | Bit:7:0   | RW     |

RedHsrPrp Reference Manual 2.5

# 4 Design Description

The following chapters describe the internals of the RED HsrPrp Core: starting with the Top Level, which is a collection of subcores, followed by the description of all subcores.

## 4.1 Top Level - RED HsrPrp

### 4.1.1.1 Parameters

The core must be parametrized at synthesis time. There are a couple of parameters which define the final behavior and resource usage of the core.

| Name               | Туре    | Size | Description                     |

|--------------------|---------|------|---------------------------------|

| NoSupport_Gen      | boolean | 1    | Support for NO (ust forward     |

| Nosupport_Gen      | Doolean | '    | no dropping, but duplication)   |

| HsrSupport_Gen     | boolean | 1    | Support for HSR                 |

| PrpSupport_Gen     | boolean | 1    | Support for PRP                 |

| HsrPrpSupport_Gen  | boolean | 1    | Support for HSR-PRP RedBox      |

| HsrHsrSupport_Gen  | boolean | 1    | Support for HSR-HSR RedBox      |

| CutThrough_Gen     | boolean | 1    | Support for Cut Through         |

| Cut mrough_Gen     | Doolean | '    | frame handling                  |

| ProxyNodeTable     | boolean | 1    | Whether the core shall be run   |

| Support_Gen        | Doolean | '    | as a RedBox                     |

| VlanSupport_Gen    | boolean | 1    | Support for VLAN tagging        |

| viansupport_Gen    | Doolean | '    | and untagging                   |

|                    |         |      | Support for Tail tagging and    |

|                    |         |      | untagging to define to send to  |

| TailTagging_Gen    | boolean | 1    | specific ports and to know      |

|                    |         |      | from which port it was re-      |

|                    |         |      | ceived                          |

| PtpSupport_Gen     | boolean | 1    | Support for PTP                 |

|                    |         |      | How many nodes it supports      |

| NrOfProxyNodes_Gen | natural | 1    | on the non-redundant net-       |

|                    |         |      | work when run as a RedBox       |

|                    |         |      | How many duplication entries    |

| NrOfEntries_Gen    | natural | 1    | shall be stored, if this number |

|                    |         |      | is lowered, chances for non-    |

|                    |                  |    | discarded duplicates is higher    |

|--------------------|------------------|----|-----------------------------------|

| HsrModeX           |                  |    | If run in HSR mode if it shall    |

| Support_Gen        | boolean          | 1  | support Mode X (duplicate         |

| 3upport_0cm        |                  |    | discarding on the ring)           |

|                    |                  |    | How many external cores can       |

|                    |                  |    | request a sequence number         |

| SeqNumber-         | <br>  natural    | 1  | from the core. The sequence       |

| OfPorts_Gen        | riacarai         | l  | number is always from the         |

|                    |                  |    | Sequence number pool of the       |

|                    |                  |    | local MAC                         |

|                    |                  |    | Shall be either 100 or 1000.      |

| LinkSpeed          | <br>  natural    | 1  | For 1000 duplication is paral-    |

| Support_Gen        | Tiatarai         |    | lelized to achieve the required   |

|                    |                  |    | throughput.                       |

| PortStatus         | boolean          | 1  | If frame and error counters       |

| Support_Gen        | Doolean          |    | shall be available in registers   |

| ClockClkPeriod     | natural          | 1  | Clock Period in Nanosecond:       |

| Nanosecond_Gen     | Tiatarai         |    | Default for 50 MHz = 20 ns        |

| StaticConfig_Gen   | boolean          | 1  | If Static Configuration or AXI    |

| StaticeOffing_Ocfi | Boolean          | '  | is used                           |

| PortAloFf_Gen      | boolean          | 1  | If Port A shall contain a IO Flip |

| TOTAIOTI_OeT       | Doolean          |    | Flop.                             |

| PortBloFf_Gen      | boolean          | 1  | If Port B shall contain a IO Flip |

| 1 01 tB101 1_0c11  | Boolean          | '  | Flop.                             |

| PortCloFf_Gen      | boolean          | 1  | If Port C shall contain a IO Flip |

| 1 6116161 1_6611   | Boolean          | '  | Flop.                             |

| AxiAddressRange    | std_logic_vector | 32 | AXI Base Address                  |

| Low_Gen            | 364_10916_100601 | 02 |                                   |

| AxiAddressRange    |                  |    | AXI Base Address plus Regis-      |

| High_Gen           | std_logic_vector | 32 | terset Size                       |

| gee                |                  |    | Default plus 0xFFFF               |

|                    |                  |    | If in Testbench simulation        |

| Sim_Gen            | boolean          | 1  | mode:                             |

|                    |                  |    | true = Simulation, false =        |

|                    |                  |    | Synthesis                         |

Table 5: Parameters

## 4.1.1.2 Structured Types

#### 4.1.1.2.1 Red\_SeqReq\_Type

Defined in Red\_Package.vhd of library RedLib

This is the type used for sequence number requesting by thirdparty cores.

| Field Name | Туре             | Size | Description                    |

|------------|------------------|------|--------------------------------|

|            |                  |      | Source Id of the port request- |

| SrcId      | std logic vector | 4    | ing a sequence number, for     |

| Siciu      | sta_logic_vector | 4    | external requesters alsways    |

|            |                  |      | OxO                            |

Table 6: Red\_SeqReq\_Type

### 4.1.1.2.2 Red\_SeqReqVal\_Type

Defined in Red\_Package.vhd of library RedLib

This is the type used for valid flags of sequence number requesting by thirdparty cores.

| Field Name | Туре      | Size | Description   |

|------------|-----------|------|---------------|

| Req_Val    | std_logic | 1    | Request valid |

Table 7: Red\_SeqReqVal\_Type

### 4.1.1.2.3 Red\_SeqResp\_Type

Defined in Red\_Package.vhd of library RedLib

This is the type used for sequence number requesting by thirdparty cores.

| Field Name | Туре             | Size | Description                                            |  |  |

|------------|------------------|------|--------------------------------------------------------|--|--|

| SeqNr      | std_logic_vector | 16   | The sequence number to be used by the thirdparty cores |  |  |

Table 8: Red\_SeqReq\_Type

### 4.1.1.2.4 Red\_SeqRespVal\_Type

Defined in Red Package.vhd of library RedLib

This is the type used for valid flags of sequence number requesting by thirdparty cores.

| Field Name | Туре      | Size | Description    |

|------------|-----------|------|----------------|

| Resp_Val   | std_logic | 1    | Response valid |

Table 9: Red\_SeqReqVal\_Type

## 4.1.1.2.5 Red\_HsrPrpStaticConfig\_Type

Defined in Red\_HsrPrpAddrPackage.vhd of library RedLib This is the type used for static configuration.

| Field Name      | Туре                 | Size | Description                                                            |

|-----------------|----------------------|------|------------------------------------------------------------------------|

| OwnMac          | Common_<br>Byte_Type | 6    | The MAC of the node. Used for supervision frames and discarding        |

| RedMode         | Red_Mode_Type        | 1    | Redundancy Mode: Hsr_E Prp_E HsrPrp_E HsrHsr_E No_E                    |

| RedBoxNetId     | std_logic_vector     | 3    | RedBox Network Identifier for HSR-PRP mode                             |

| RedBoxId        | std_logic_vector     | 4    | RedBox Identifier for HSR-PRP mode                                     |

| PromiscuousMode | std_logic            | 1    | If Promiscuous mode shall be active for Port C                         |

| NoForward       | std_logic            | 1    | If forwarding between Ports A<br>& B shall be disabled                 |

| TailTagging     | std_logic            | 1    | If tail tagging shall be used for frames to and from Port C            |

| PrpUntagging    | std_logic            | 1    | If frames from Port A and B shall be untagged when forwarded to Port C |

| CutThough       | std_logic            | 1    | If frames shall be processed in cut through mode                       |

| Vlan       | Red_Vlan_Type | 1 | The Pcp,Dei and Vid of the VLAN |

|------------|---------------|---|---------------------------------|

| VlanEnable | std_logic     | 1 | If VLAN shall be used           |