|

Ptp_Tsu_Flyer.pdf Size : 150.105 Kb Type : pdf |

|

Ptp_Tsu_ReferenceManual.pdf Size : 1504.647 Kb Type : pdf |

|

Ptp_Tsu_10GigabitExtension.pdf Size : 532.889 Kb Type : pdf |

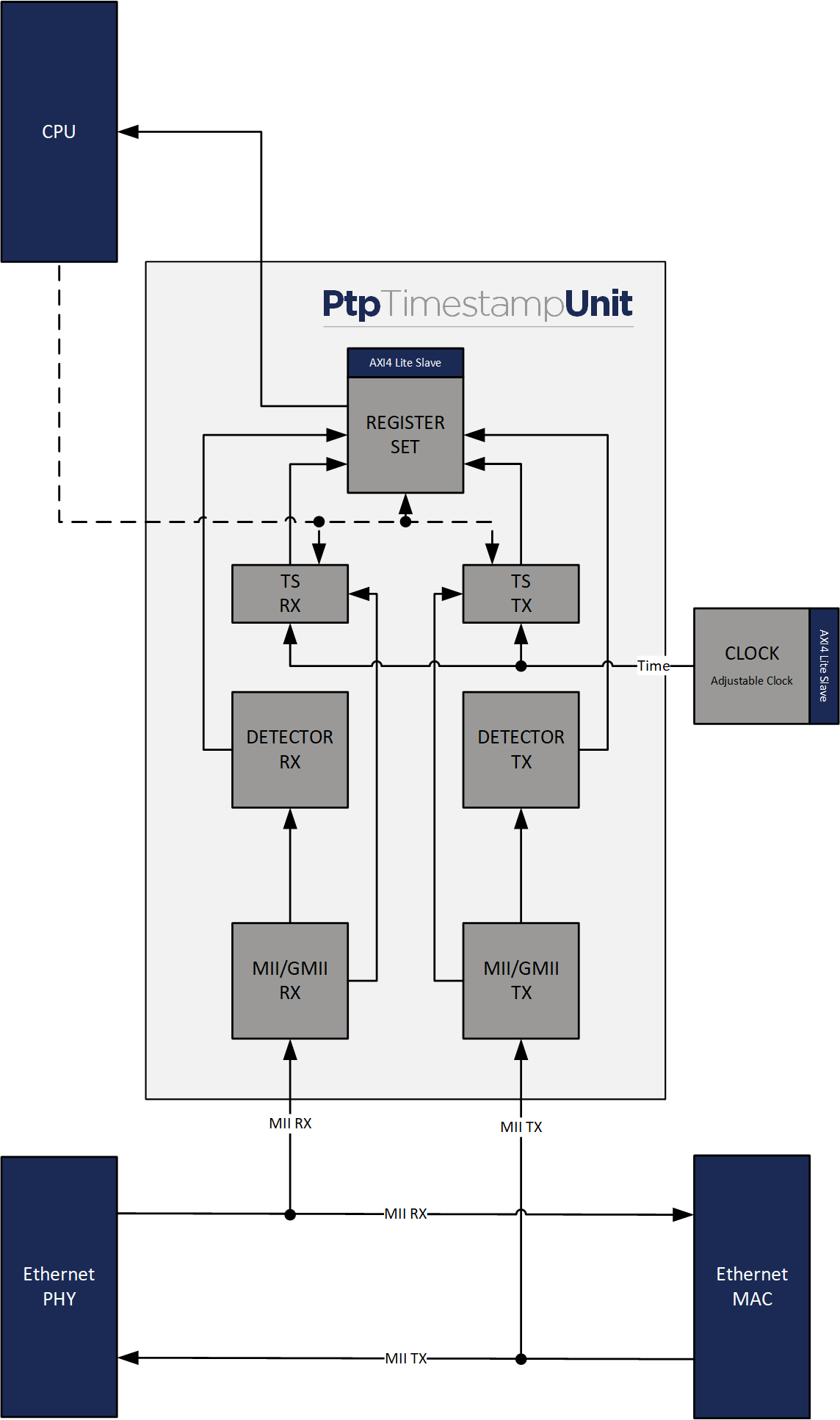

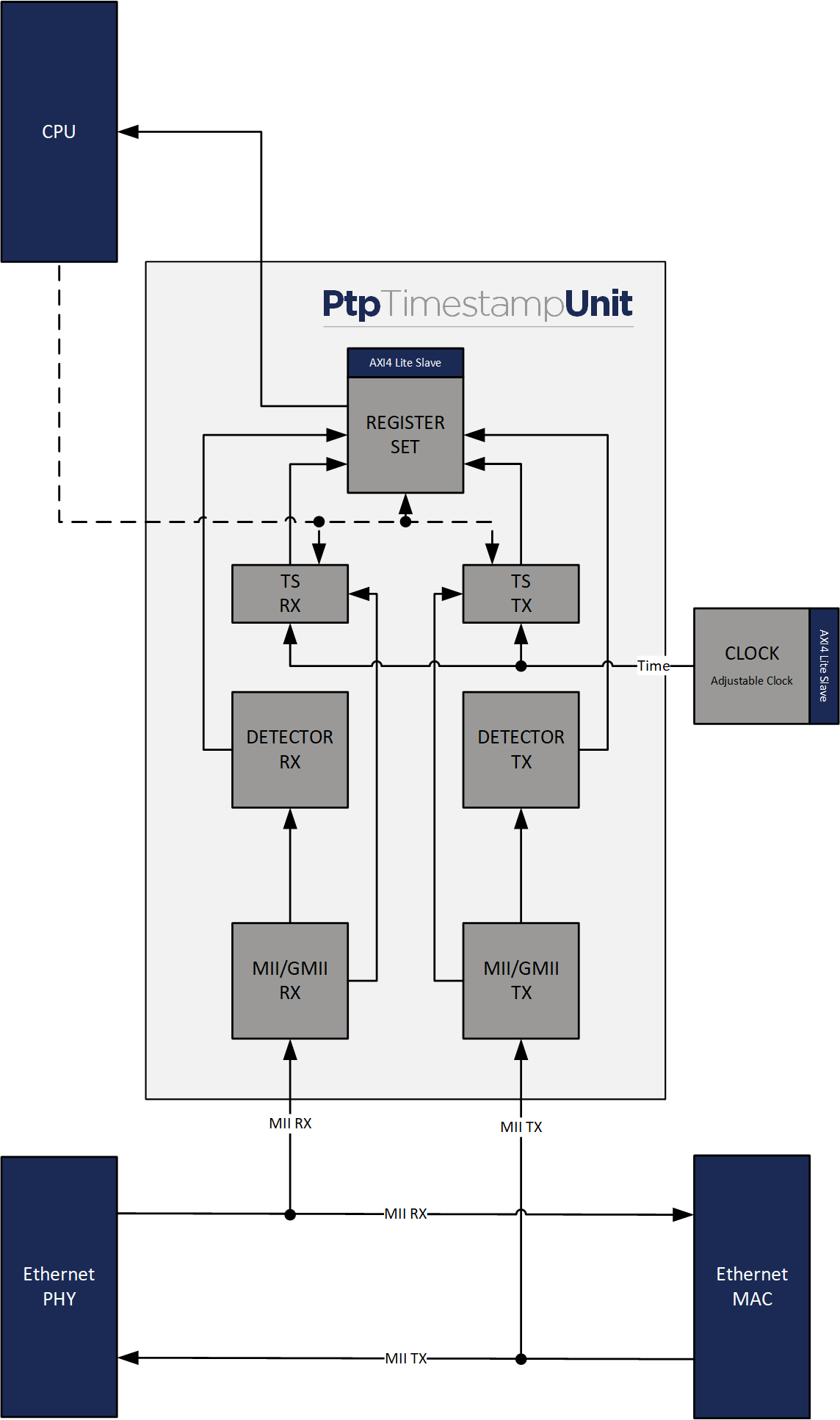

NetTimeLogic’s PTP Timestamp Unit is an implementation of a single port Frame Timestamp Unit (TSU) according to IEEE1588-2019/2008(PTP). It detects PTP frames on a (R)(G)MII tap and timestamps PTP event frames based on a Counter Clock and provides them delay compensated to a PTP Software stack (e.g. PTPd, PTP4l, etc…). The Timestamp Unit can work as PTP Ordinary Clock (OC) as Master and Slave; it can also be used to build a PTP Boundary Clock (BC) by having multiple instances of the IP core connected to multiple Ethernet ports. All configuration can be written, and timestamps read via an AXI4Light-Slave Register interface.

The IP core comes with a Linux Driver for the AMD(R) Zynq 70xx (and as template for integration into other SoCs with AXI interface)

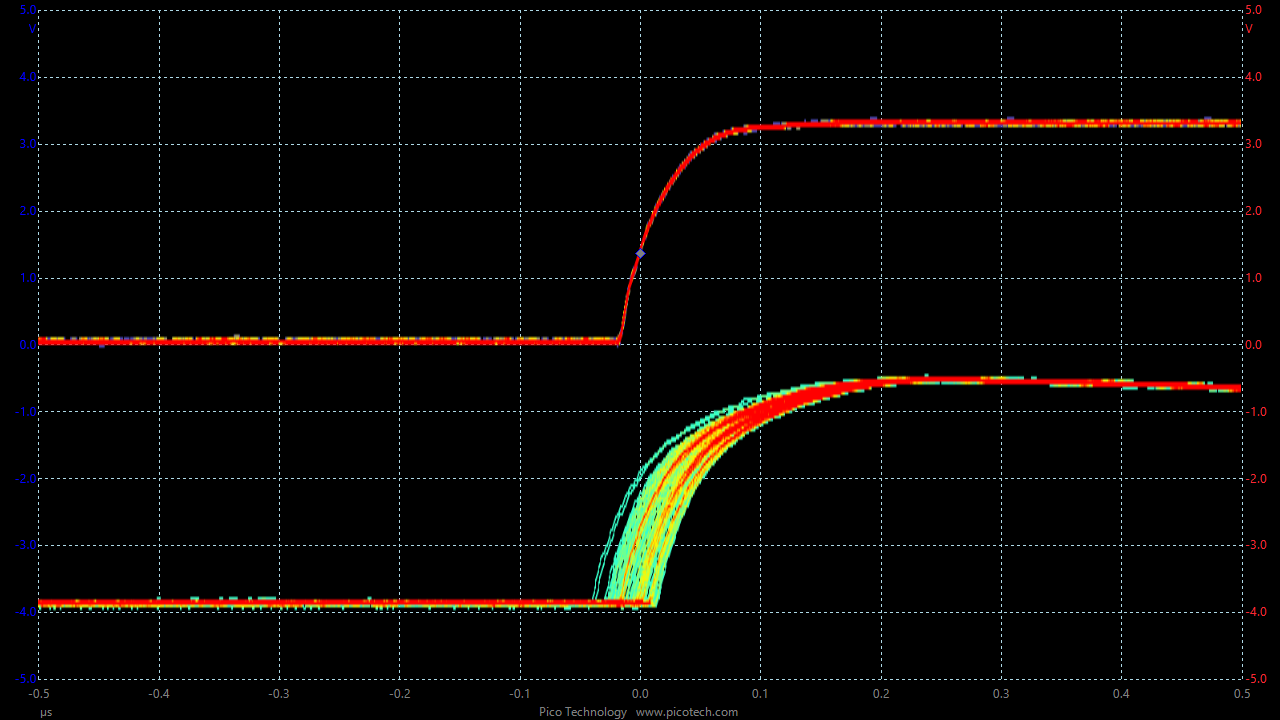

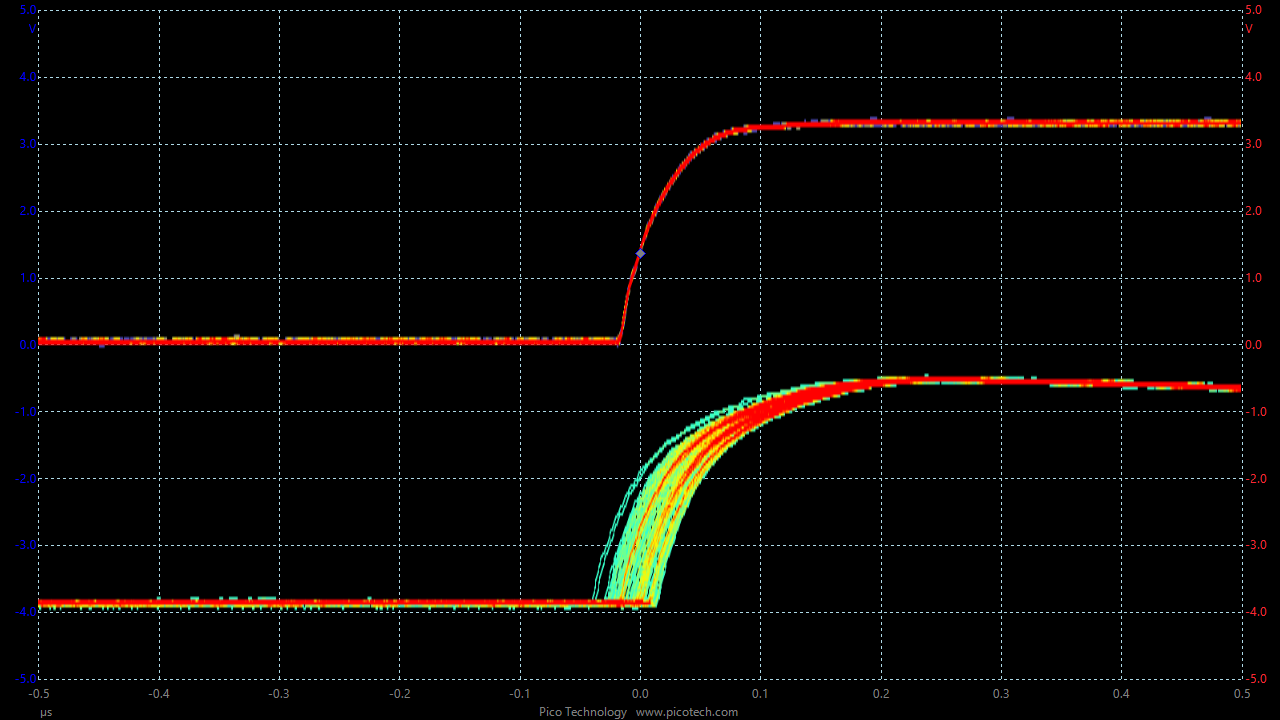

100ns per division on oscilloscope

The synchronization accuracy achieved with a 50MHz oscillator is around +/-25ns

There are different licensing possibilities (more info here). All prices are in US Dollars without VAT, all prices are one-time fees, no royalties apply:

All prices are non-binding estimates – please use the contact form for definitive pricing and lead-time information.

Evaluation binaries available for Digilent's Arty Z7 development boards (with ptp4l as software stack) or as Modelsim(R) precompiled libraries => contact us for free access

|

Ptp_Tsu_Flyer.pdf Size : 150.105 Kb Type : pdf |

|

Ptp_Tsu_ReferenceManual.pdf Size : 1504.647 Kb Type : pdf |

|

Ptp_Tsu_10GigabitExtension.pdf Size : 532.889 Kb Type : pdf |