# **Ptp10GExtension**

**TSU Reference Manual**

| Product Info    |            |

|-----------------|------------|

| Product Manager | Sven Meier |

| Author(s)       | Sven Meier |

| Reviewer(s)     | -          |

| Version         | 0.2        |

| Date            | 25.10.2024 |

# **Copyright Notice**

Copyright © 2025 NetTimeLogic GmbH, Switzerland. All rights reserved. Unauthorized duplication of this document, in whole or in part, by any means, is prohibited without the prior written permission of NetTimeLogic GmbH, Switzerland.

All referenced registered marks and trademarks are the property of their respective owners

# Disclaimer

The information available to you in this document/code may contain errors and is subject to periods of interruption. While NetTimeLogic GmbH does its best to maintain the information it offers in the document/code, it cannot be held responsible for any errors, defects, lost profits, or other consequential damages arising from the use of this document/code.

NETTIMELOGIC GMBH PROVIDES THE INFORMATION, SERVICES AND PROD-UCTS AVAILABLE IN THIS DOCUMENT/CODE "AS IS," WITH NO WARRANTIES WHATSOEVER. ALL EXPRESS WARRANTIES AND ALL IMPLIED WARRANTIES, INCLUDING WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTIC-ULAR PURPOSE, AND NON-INFRINGEMENT OF PROPRIETARY RIGHTS ARE HEREBY DISCLAIMED TO THE FULLEST EXTENT PERMITTED BY LAW. IN NO EVENT SHALL NETTIMELOGIC GMBH BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, CONSEQUENTIAL, SPECIAL AND EXEMPLARY DAMAGES, OR ANY DAMAGES WHATSOEVER, ARISING FROM THE USE OR PERFORMANCE OF THIS DOCUMENT/CODE OR FROM ANY INFORMATION, SERVICES OR PRODUCTS PROVIDED THROUGH THIS DOCUMENT/CODE, EVEN IF NETTIMELOGIC GMBH HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

IF YOU ARE DISSATISFIED WITH THIS DOCUMENT/CODE, OR ANY PORTION THEREOF, YOUR EXCLUSIVE REMEDY SHALL BE TO CEASE USING THE DOCU-MENT/CODE.

# Overview

NetTimeLogic's PTP Timestamp Unit allows to create a PTP Ordinary Clock or Boundary Clock with OneStep support according to IEEE1588-2019/2008 (PTP). It takes timestamp for PTP frames and allows additional OneStep timestamp insertion if intercepting the XGMII. This Document describes the 10 Gigabit Extension to the PTP Timestamp Unit

# **Key Features:**

- PTP Timestamp Unit according to IEEE1588-2019/2008 and IEEE802.1AS

- PTP frame detection and parsing

- Optional Passthrough Mode

- Optional PTP One Step functionality

- PTP event frame timestamping

- Optional Meta Information to safely match timestamps and frames

- Optional timestamp buffers for each frame type to handle also bursts of frames and high PTP frame rates (requires Meta Information)

- Taps path between MAC and PHY

- Synchronization accuracy: +/- 25ns

- Support for Layer 2 (Ethernet) and Layer 3 (Ipv4 and IPv6), Peer to Peer (P2P) and End to End (E2E).

- Support for Unicast Frames

- Master and Slave support

- Full line speed

- AXI4Lite register set

- Configurable Interrupt

- PHY Delay compensation with automatic link speed detection (in driver)

- XGMII Interface support

- Timestamp resolution with 50 MHz system clock: 10ns

- Optional High-Resolution Timestamping with 250MHz: 4ns

# **Revision History**

This table shows the revision history of this document.

| Version | Date       | Revision                            |

|---------|------------|-------------------------------------|

| 0.1     | 04.03.2022 | First draft                         |

| 0.2     | 25.10.2024 | IEEE1588-2008 => IEEE1588-2019/2008 |

Table 1: Revision History

# Content

| 1     | INTRODUCTION                   | 8  |

|-------|--------------------------------|----|

| 1.1   | Context Overview               | 8  |

| 1.2   | Function                       | 9  |

| 1.3   | Architecture                   | 9  |

| 2     | DESIGN DESCRIPTION             | 13 |

| 2.1   | Top Level – PTP Ordinary Clock | 13 |

| 2.2   | Design Parts                   | 21 |

| 2.2.1 | XGMII Interface Adapter        | 21 |

| 2.2.2 | 2 Arbiter                      | 24 |

| 2.2.3 | 3 PTP Filter and Splitter      | 26 |

| 2.2.4 | 4 TX Conversion FIFO           | 28 |

| 2.2.5 | 5 RX Conversion FIFO           | 31 |

| 2.2.6 | 6 Forwarding FIFO              | 34 |

| 2.3   | Clocking and Reset Concept     | 36 |

| 2.3.1 | Clocking                       | 36 |

| 2.3.2 | 2 Reset                        | 37 |

# Definitions

| Definitions       |                                                                                           |

|-------------------|-------------------------------------------------------------------------------------------|

| Ordinary Clock    | A synchronization end node according to IEEE1588 that<br>can take a Master and Slave role |

| Transparent Clock | A network node (Switch) that is IEEE1588 aware and com-<br>pensates network jitter        |

| Default Profile   | PTP Profile according to IEEE1588                                                         |

| Power Profile     | PTP Profile according to C37.238-2011                                                     |

| Utility Profile   | PTP Profile according to IEC 61850 9-3                                                    |

| TSN Profile       | PTP Profile according to IEEE802.1AS                                                      |

Table 2: Definitions

# Abbreviations

| Abbreviations |                                                     |

|---------------|-----------------------------------------------------|

| AXI           | AMBA4 Specification (Stream and Memory Mapped)      |

| IRQ           | Interrupt, Signaling to e.g. a CPU                  |

| PRP           | Parallel Redundancy Protocol (IEC 62439-3)          |

| HSR           | High-availability Seamless Redundancy (IEC 62439-3) |

| PTP           | Precision Time Protocol (See also IEEE1588)         |

| МАС           | Media Access Controller                             |

| PHY           | Physical Media Access Controller                    |

| OC            | Ordinary Clock                                      |

| ТС            | Transparent Clock                                   |

| TS            | Timestamp                                           |

| ETH           | Ethernet                                            |

| ТВ            | Testbench                                           |

| LUT           | Look Up Table                                       |

| FF            | Flip Flop                                           |

| RAM  | Random Access Memory                     |

|------|------------------------------------------|

| ROM  | Read Only Memory                         |

| FPGA | Field Programmable Gate Array            |

| VHDL | Hardware description Language for FPGA's |

Table 3: Abbreviations

# 1 Introduction

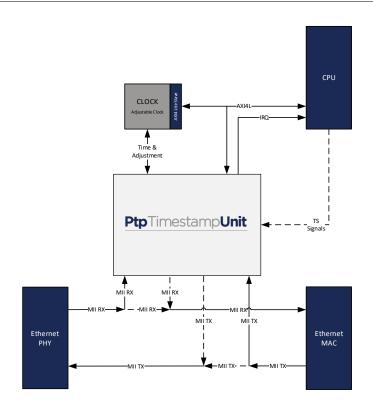

## 1.1 Context Overview

The PTP Timestamp Unit is meant as a co-processor handling PTP timestamps on a network port. It taps or passes through the Media Independent Interface ((R)(G)MII) on the Ethernet path between the MAC, Switch or Redundancy core and PHYs where it detects and timestamps PTP traffic and optionally stores meta information and buffers the timestamps or optionally does OneStep frame modifications. It compensates the timestamps for the PHY delays and generates a configurable interrupt whenever a timestamp is ready for a specific frame type. The CPU shall use these timestamps in a PTP software stack like PTP4I, PTPd, etc. to synchronize the clock which is the base for the timestamps (Slave) or to distribute time (Master).

The PTP Timestamp Unit is specifically designed for Systems on Chip (SoC) where a CPU and FPGA part are often combined on the same silicon. In addition to the MII tap, there is also a possibility to pass the MII through the TSU for OneStep operation also there is a possibility to feed PTP timestamp signals from another source (e.g. PTP detector in a MAC), this is possible with e.g. a Xilinx® Zynq device. In this case the frame processing is omitted and only the timestamp and register part is used.

The PTP Timestamp Unit is designed to work in cooperation with the Counter Clock core from NetTimeLogic (not a requirement). It contains an AXI4Lite slave for configuration, status supervision ad fetching of the timestamps from a CPU.

## 1.2 Function

The PTP Timestamp Unit part is a PTP TSU according to IEEE1588-2019/2008 and IEEE802.1AS. It detects PTP frames when they pass the MII and takes timestamps of PTP event frames. It also compensates the PHY delays so the timestamps reflect the time when the PTP frames entered or left the PHY on the cable, which is the defined timestamp point according to IEEE1588-2019/2008. It can optionally also insert timestamps on the fly for OneStep operation

## 1.3 Architecture

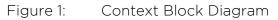

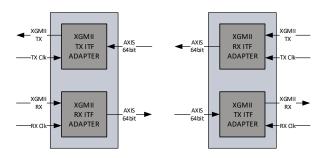

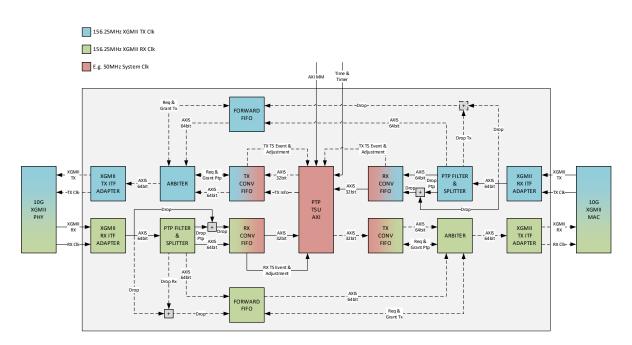

For 10 Gigabit the PTP Timestamp Unit was extended by a 10G XGMII wrapper which basically handles all 10G traffic and just connects the PTP Timestamp Unit to it so it can inject PTP traffic and receives PTP traffic only, allowing the PTP core to run on a much slower link speed rate since PTP message rates are well below 10G. This resulted in the following Architecture:

Figure 2: Architecture Block Diagram

#### XGMII TX Interface Adapter

The XGMII TX Interface Adapter converts a 64bit AXI stream running on the XGMII clock (156,25 MHz) to XGMII stream in 64bit mode (without DDR). It generates the interframe gap of minimum 12 byte times, adds the Preamble and Start of Frame Delimiter (SFD) and encodes the incoming AXI stream to the XGMII interface (64bit data, 8bit control) using the control lines and special characters according to the XGMII specification. Start of frame shall always be on Lane 0. It is instantiated on the TX side of the PCS and on the RX side of the MAC.

#### XGMII RX Interface Adapter

The XGMII RX Interface Adapter converts a XGMII stream in 64bit mode (without DDR) to a 64bit AXI stream running on the XGMII clock (156,25 MHz). It removes the Preamble and Start of Frame Delimiter (SFD) and decodes the incoming XGMII stream (64bit data, 8bit control) to the AXI stream interface using the control lines and special characters according to the XGMII specification. Start of frame shall always be on Lane 0 (or 4).

It is instantiated on the RX side of the PCS and on the TX side of the MAC.

#### Arbiter

The Arbiter arbitrates between the 10G forwarding path from the MAC to the PCS and the PTP TSU core. It has request and grant lines and will do arbitration in a round robin manner so that no path is starving.

#### **PTP Filter and Splitter**

This module splits the 64bit AXI stream coming from the XGMII RX Interface Adapter into a 64bit AXI stream for the TSU and a 64bit AXI stream for the forwarding path. It contains a frame parser which will check if a frame is a PTP frame or not and will assert the according drop signal towards one of the connected FIFOs.

#### **TX Conversion FIFO**

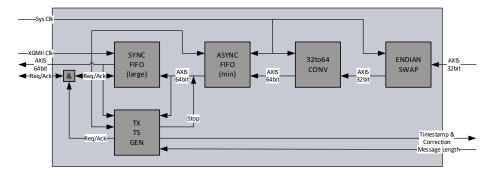

The TX Conversion FIFO has multiple functionalities. It converts the 32bit AXI stream from the PTP TSU to a 64bit AXI stream and uses an asynchronous storeand-forward FIFO to do the clock domain crossing and to be able to provide the frame with 10G towards the XGMII TX Interface Adapter.

In addition, it detects the start of the frame and signals this to the PTP core (this is done here since the path towards the XGMII Interface adapter is fully deterministic and it is also a preparation for the one-step mode). The challenge here is to align the timestamp event signal to the frame without inserting additional jitter.

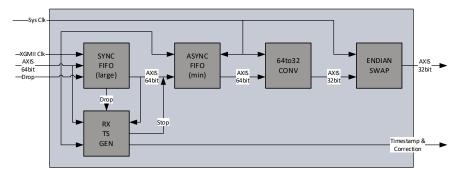

#### **RX Conversion FIFO**

The RX Conversion FIFO has also multiple functionalities. It converts the 64bit AXI stream from the XGMII Interface Adapter to a 32bit AXI stream and uses an asynchronous store-and-forward FIFO to do the clock domain crossing and to be able to handle the frame with 10G from the XGMII RX Interface Adapter before converting to the slower clock speed. It also has a drop input which is used to explicitly drop the incoming frame. This is used by the PTP Filter and Splitter to drop Non-PTP frames towards the PTP TSU.

In addition, it detects the start of the frame and signals this to the PTP core (this is done here since the path from the XGMII Interface adapter is fully deterministic). The challenge here is to align the timestamp event signal to the frame without inserting additional jitter.

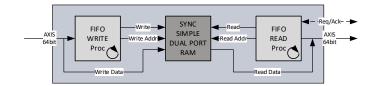

#### **Forwarding FIFOs**

This is a store-and-forward or cut-through frame drop FIFO, which means it can drop a whole frame if it runs into an overflow condition. This is required since the PTP core will use a small amount of bandwidth which could lead to an overload condition. It also has a drop input which is used to explicitly drop the incoming frame. This is used by the PTP Filter and Splitter to drop PTP frames on the forwarding path. It also has a request and grant signal which is used for the arbitration. It is instantiated on the RX and TX forwarding path.

#### **PTP Timestamp Unit**

This is the actual PTP Timestamp Unit IP core from NetTimeLogic, it receives and transmits PTP frames via 32bit AXI stream interfaces and has timestamp inputs which can trigger a TX or RX timestamp in the core when the SFD on the corresponding path was detected, it provides the TX frame length and receives the calculated RX and TX delays with the timestamp indications.

# 2 Design Description

The following chapters describe the internals of the PTP Timestamp Unit 10G: starting with the Top Level, which is a collection of subcores, followed by the description of all subcores.

# 2.1 Top Level – PTP Ordinary Clock

#### 2.1.1.1 Parameters

The core must be parametrized at synthesis time. It has the same parameters as the Non-10G version, additionally the following parameters are available.

| Name                           | Туре    | Size | Description                 |

|--------------------------------|---------|------|-----------------------------|

| RxDelayNanosecond<br>10000_Gen | integer | 1    | PHY receive delay (10Gbit)  |

| TxDelayNanosecond<br>10000_Gen | integer | 1    | PHY transmit delay (10Gbit) |

Table 4:Parameters

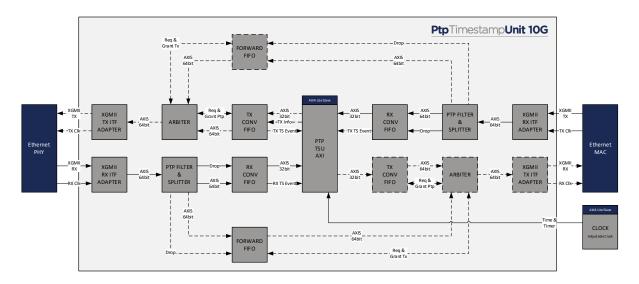

## 2.1.1.2 Entity Block Diagram

#### Figure 3: PTP Timestamp Unit 10G

#### 2.1.1.3 Entity Description

#### XGMII TX Interface Adapter

The XGMII TX Interface Adapter converts a 64bit AXI stream running on the XGMII clock (156,25 MHz) to XGMII stream in 64bit mode (without DDR). It generates the interframe gap of minimum 12 byte times, adds the Preamble and Start of Frame Delimiter (SFD) and encodes the incoming AXI stream to the XGMII interface (64bit data, 8bit control) using the control lines and special characters according to the XGMII specification. Start of frame shall always be on Lane 0. It is instantiated on the TX side of the PCS and on the RX side of the MAC. See 2.2.1 for more details.

#### XGMII RX Interface Adapter

The XGMII RX Interface Adapter converts a XGMII stream in 64bit mode (without DDR) to a 64bit AXI stream running on the XGMII clock (156,25 MHz). It removes the Preamble and Start of Frame Delimiter (SFD) and decodes the incoming XGMII stream (64bit data, 8bit control) to the AXI stream interface using the control lines and special characters according to the XGMII specification. Start of frame shall always be on Lane 0 (or 4).

It is instantiated on the RX side of the PCS and on the TX side of the MAC. See 2.2.1 for more details.

#### Arbiter

The Arbiter arbitrates between the 10G forwarding path from the MAC to the PCS and the PTP TSU core. It has request and grant lines and will do arbitration in a round robin manner so that no path is starving.

See 2.2.2 for more details.

#### **PTP Filter and Splitter**

This module splits the 64bit AXI stream coming from the XGMII RX Interface Adapter into a 64bit AXI stream for the TSU and a 64bit AXI stream for the forwarding path. It contains a frame parser which will check if a frame is a PTP frame or not and will assert the according drop signal towards one of the connected FIFOs.

See 2.2.3 for more details.

#### **TX Conversion FIFO**

The TX Conversion FIFO has multiple functionalities. It converts the 32bit AXI stream from the PTP TSU to a 64bit AXI stream and uses an asynchronous store-

and-forward FIFO to do the clock domain crossing and to be able to provide the frame with 10G towards the XGMII TX Interface Adapter.

In addition, it detects the start of the frame and signals this to the PTP core (this is done here since the path towards the XGMII Interface adapter is fully deterministic and it is also a preparation for the one-step mode). The challenge here is to align the timestamp event signal to the frame without inserting additional jitter. See 2.2.4 for more details.

#### **RX Conversion FIFO**

The RX Conversion FIFO has also multiple functionalities. It converts the 64bit AXI stream from the XGMII Interface Adapter to a 32bit AXI stream and uses an asynchronous store-and-forward FIFO to do the clock domain crossing and to be able to handle the frame with 10G from the XGMII RX Interface Adapter before converting to the slower clock speed. It also has a drop input which is used to explicitly drop the incoming frame. This is used by the PTP Filter and Splitter to drop Non-PTP frames towards the PTP TSU.

In addition, it detects the start of the frame and signals this to the PTP core (this is done here since the path from the XGMII Interface adapter is fully deterministic). The challenge here is to align the timestamp event signal to the frame without inserting additional jitter.

See 2.2.5 for more details.

#### **Forwarding FIFOs**

This is a store-and-forward or cut-through frame drop FIFO, which means it can drop a whole frame if it runs into an overflow condition. This is required since the PTP core will use a small amount of bandwidth which could lead to an overload condition. It also has a drop input which is used to explicitly drop the incoming frame. This is used by the PTP Filter and Splitter to drop PTP frames on the forwarding path. It also has a request and grant signal which is used for the arbitration. It is instantiated on the RX and TX forwarding path. See 2.2.6 for more details.

#### **PTP Ordinary Clock**

This is the actual PTP Timestamp Unit IP core from NetTimeLogic, it receives and transmits PTP frames via 32bit AXI stream interfaces and has timestamp inputs which can trigger a TX or RX timestamp in the core when the SFD on the corresponding path was detected, it provides the TX frame length and receives the calculated RX and TX delays with the timestamp indications.

See the PTP Timestamp Unit Manual for details.

## 2.1.1.4 Entity Declaration

| Name               | Dir      | Туре    | Size | Description            |  |  |

|--------------------|----------|---------|------|------------------------|--|--|

|                    | Generics |         |      |                        |  |  |

| General            |          |         |      |                        |  |  |

|                    |          |         |      | Whether the MII is     |  |  |

| PassThrough_Gen    | -        | boolean | 1    | passed through or      |  |  |

|                    |          |         |      | tapped                 |  |  |

|                    |          |         |      | Whether OnStep         |  |  |

|                    |          |         | 1    | support shall be       |  |  |

| OneStepSupport_Gen | -        | boolean | 1    | there, requires pass   |  |  |

|                    |          |         |      | through                |  |  |

| DefaultProfile     |          |         |      | Support for Default    |  |  |

| Support_Gen        | -        | boolean | 1    | Profile                |  |  |

| PowerProfile       |          |         |      | Support for Power      |  |  |

| Support_Gen        | -        | boolean | 1    | Profile                |  |  |

| UtilityProfile     |          |         |      | Support for Utility    |  |  |

| Support_Gen        | -        | boolean | 1    | Profile                |  |  |

| TsnProfile         |          |         |      | Support for            |  |  |

| Support_Gen        | -        | boolean | 1    | IEEE802.1AS            |  |  |

| UnicastProfile     |          |         |      | Support for Unicast    |  |  |

| Support_Gen        | -        | boolean | 1    | PTP messages           |  |  |

|                    |          |         | 1    | Support for Layer 2    |  |  |

| Layer2Support_Gen  | -        | boolean | 1    | Mapping                |  |  |

| Lay-               |          |         | 1    | Support for IPv4       |  |  |

| er3v4Support_Gen   | -        | boolean | 1    | Mapping                |  |  |

| Lay-               |          | baalaan | 1    | Support for IPv6       |  |  |

| er3v6Support_Gen   | -        | boolean | I    | Mapping                |  |  |

| DodTogSupport Can  |          | boolean | 1    | If HSR or FRER tags    |  |  |

| RedTagSupport_Gen  | -        |         |      | shall be detected      |  |  |

|                    |          |         |      | If Meta Information    |  |  |

|                    |          | boolean |      | shall be stored with   |  |  |

| MetaInfo_Gen       | - bo     |         | 1    | the timestamp (this    |  |  |

|                    |          |         |      | is required if Buffer- |  |  |

|                    |          |         |      | ing shall be done)     |  |  |

|                                 |   |         |   | Buffer Depth for   |

|---------------------------------|---|---------|---|--------------------|

|                                 | - |         |   |                    |

|                                 |   |         |   | Delay Request RX   |

| DelayReqRxBuffer                |   | natural | 1 | Timestamps. 0 = No |

| Depth_Gen                       |   |         |   | buffering (>0 re-  |

|                                 |   |         |   | quires Metaln-     |

|                                 |   |         |   | fo_Gen = true)     |

|                                 |   |         |   | Buffer Depth for   |

|                                 |   |         |   | Delay Request TX   |

| DelayReqTxBuffer                | - | natural | 1 | Timestamps. 0 = No |

| Depth_Gen                       |   |         |   | buffering (>0 re-  |

|                                 |   |         |   | quires Metaln-     |

|                                 |   |         |   | fo_Gen = true)     |

|                                 |   |         |   | Buffer Depth for   |

|                                 |   |         |   | Peer Delay Request |

| PDelayReqRxBuffer               | - | natural | 1 | RX Timestamps. 0 = |

| Depth_Gen                       |   |         |   | No buffering (>0   |

|                                 |   |         |   | requires Metaln-   |

|                                 |   |         |   | fo_Gen = true)     |

|                                 |   |         |   | Buffer Depth for   |

|                                 |   |         |   | Peer Delay Request |

| PDelayReqTxBuffer               |   | natural | 1 | TX Timestamps. 0 = |

| Depth_Gen                       | - | natural | I | No buffering (>0   |

|                                 |   |         |   | requires Metaln-   |

|                                 |   |         |   | fo_Gen = true)     |

|                                 |   |         |   | Buffer Depth for   |

|                                 |   |         |   | Peer Delay Re-     |

|                                 |   |         |   | sponse RX          |

| PDelayRespRxBuffer              | - | natural | 1 | Timestamps. 0 = No |

| Depth_Gen                       |   |         |   | buffering (>0 re-  |

|                                 |   |         |   | quires Metaln-     |

|                                 |   |         |   | fo_Gen = true)     |

|                                 | 1 |         |   | Buffer Depth for   |

|                                 |   |         |   | Peer Delay Re-     |

| PDelayRespTxBuffer<br>Depth_Gen | - |         |   | sponse TX          |

|                                 |   | natural | 1 | Timestamps. 0 = No |

|                                 |   |         |   | buffering (>0 re-  |

|                                 |   |         |   | quires Metaln-     |

|                                 |   |         |   | fo_Gen = true)     |

|                                 |   |         |   |                    |

| SyncRxBuffer-                     |    |                  |    | Buffer Depth Sync<br>RX Timestamps. 0 =                                         |  |

|-----------------------------------|----|------------------|----|---------------------------------------------------------------------------------|--|

| Depth_Gen                         | -  | natural          | 1  | No buffering (>0                                                                |  |

| Depth_Oen                         |    |                  |    | requires Metaln-                                                                |  |

|                                   |    |                  |    | fo_Gen = true)                                                                  |  |

|                                   |    |                  |    | Buffer Depth for                                                                |  |

|                                   |    |                  |    | Sync TX                                                                         |  |

| SyncTxBuffer-                     | -  | natural          | 1  | Timestamps. 0 = No                                                              |  |

| Depth_Gen                         |    |                  |    | buffering (>0 re-                                                               |  |

|                                   |    |                  |    | quires Metaln-                                                                  |  |

|                                   |    |                  |    | fo_Gen = true)                                                                  |  |

| ClockClkPeriodNano-<br>second_Gen | -  | natural          | 1  | Integer Clock Period                                                            |  |

| RxDelayNanosecond<br>10000_Gen    | -  | integer          | 1  | RX Delay of the PHY<br>in Nanosecond                                            |  |

| TxDelayNanosecond                 | _  | integer          | 1  | TX Delay of the PHY                                                             |  |

| 10000_Gen                         |    | lineger          |    | in Nanosecond                                                                   |  |

| HighResSupport_Gen                | -  | boolean          | 1  | If a high-resolution<br>clock SysClkNx with<br>alignment to SysClk<br>is used   |  |

| HighResFreq<br>Multiply_Gen       | _  | natural          | 1  | Multiplication factor<br>of the high-<br>resolution clock<br>compared to SysClk |  |

| AxiAddressRange<br>Low_Gen        | -  | std_logic_vector | 32 | AXI Base Address                                                                |  |

| AxiAddressRange<br>High_Gen       | -  | std_logic_vector | 32 | AXI Base Address<br>plus Registerset<br>Size                                    |  |

| Sim_Gen                           | -  | boolean          | 1  | If in Testbench<br>simulation mode                                              |  |

| Ports                             |    |                  |    |                                                                                 |  |

| System<br>SysClk_ClkIn            | in | std_logic        | 1  | System Clock                                                                    |  |

|                                   |    | _ ~              |    | High-resolution                                                                 |  |

| SysClkNx_ClkIn                    | in | std_logic        | 1  | clock (multiple of<br>Sys Clock)                                                |  |

| SysRstN_RstIn                              | in         | std_logic        | 1  | System Reset                     |

|--------------------------------------------|------------|------------------|----|----------------------------------|

| Time Input<br>ClockTime_DatIn              | in         | Clk_Time_Type    | 1  | Adjusted PTP Clock<br>Time       |

| ClockTime_ValIn                            | in         | std_logic        | 1  | Adjusted PTP Clock<br>Time valid |

| XGMii RX Clk/Rst Input<br>XGMiiRxClk_ClkIn | in         | std_logic        | 1  | RX Clock                         |

| <br>XGMiiRxRstN_RstIn                      | in         | std_logic        | 1  | Reset aligned with<br>RX Clock   |

| XGMii TX Clk/Rst Input<br>XGMiiTxClk_ClkIn | in         | std_logic        | 1  | TX Clock                         |

| XGMiiTxRstN_RstIn                          | in         | std_logic        | 1  | Reset aligned with<br>TX Clock   |

| XGMii RX Data Input/O                      | utput      |                  | 1  |                                  |

| XGMiiRxCtl_Ena                             | in/<br>out | std_logic        | 8  | RX Data valid                    |

| XGMiiRxData_Dat                            | in/<br>out | std_logic_vector | 64 | RX Data                          |

| XGMii TX Data Input/O                      | utput      |                  |    |                                  |

| XGMiiTxCtl_Ena                             | in/<br>out | std_logic        | 1  | TX Data valid                    |

| XGMiiTxData_Dat                            | in/<br>out | std_logic_vector | 64 | TX Data                          |

| AXI4 Lite Slave                            |            |                  |    |                                  |

| AxiWriteAddrValid<br>_ValIn                | in         | std_logic        | 1  | Write Address Valid              |

| AxiWriteAddrReady<br>_RdyOut               | out        | std_logic        | 1  | Write Address<br>Ready           |

| AxiWriteAddrAddress<br>_AdrIn              | in         | std_logic_vector | 32 | Write Address                    |

| AxiWriteAddrProt<br>_DatIn                 | in         | std_logic_vector | 3  | Write Address<br>Protocol        |

| AxiWriteDataValid<br>Valln                 | in         | std_logic        | 1  | Write Data Valid                 |

| AxiWriteDataReady<br>_RdyOut               | out        | std_logic        | 1  | Write Data Ready                 |

| AxiWriteDataData<br>_DatIn                 | in         | std_logic_vector | 32 | Write Data                       |

| AxiWriteDataStrobe                         | in         | std_logic_vector | 4  | Write Data Strobe                |

| AxiWriteRespValid<br>_ValOut               | out        | std_logic        | 1  | Write Response<br>Valid          |

| AxiWriteRespReady<br>_RdyIn     | in  | std_logic        | 1  | Write Response<br>Ready  |

|---------------------------------|-----|------------------|----|--------------------------|

| AxiWriteResp<br>Response_DatOut | out | std_logic_vector | 2  | Write Response           |

| AxiReadAddrValid<br>_Valln      | in  | std_logic        | 1  | Read Address Valid       |

| AxiReadAddrReady<br>_RdyOut     | out | std_logic        | 1  | Read Address<br>Ready    |

| AxiReadAddrAddress<br>Adrln     | in  | std_logic_vector | 32 | Read Address             |

| <br>AxiReadAddrProt<br>DatIn    | in  | std_logic_vector | 3  | Read Address<br>Protocol |

| AxiReadDataValid<br>ValOut      | out | std_logic        | 1  | Read Data Valid          |

|                                 | in  | std_logic        | 1  | Read Data Ready          |

| AxiReadData<br>Response_DatOut  | out | std_logic_vector | 2  | Read Data                |

| AxiReadDataData<br>_DatOut      | out | std_logic_vector | 32 | Read Data Re-<br>sponse  |

| Interrupt Output                |     | ·                |    |                          |

| Irq_EvtOut                      | out | std_logic        | 1  | Level high Interrupt     |

Table 5:

PTP Timestamp Unit XGMII

## 2.2 Design Parts

The PTP Timestamp Unit core consists of a couple of subcores. Each of the subcores itself consist again of smaller function block. The following chapters describe these subcores and their functionality.

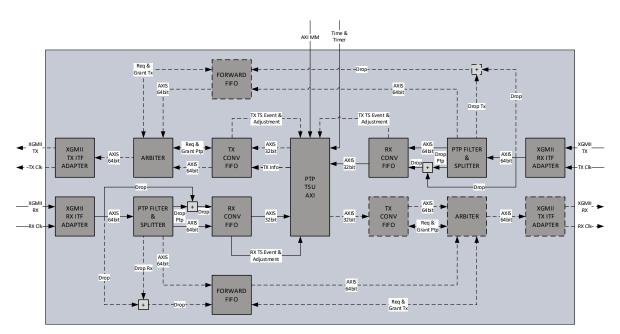

## 2.2.1 XGMII Interface Adapter

#### 2.2.1.1 Entity Block Diagram

Figure 4: XGMII Interface Adapter

#### 2.2.1.2 Entity Description

To have a deterministic delay, to have only a minimum of clock domains in the design and to save resources, the AXI stream interface and the XGMII interface shall run on the same clock per direction (RX/TX).

There are two different versions of the interface adapter, a MAC and PHY side version. One is connected to the PHY and the other one to the MAC. Internally the same components are used to handle XGMII, it is only a naming scheme.

For the interface adapter, all clocks are inputs, even if on a higher level the clock is passed through, so it will be also an output of the overall design.

#### XGMII TX Interface Adapter

The XGMII TX Interface Adapter converts a 64bit AXI stream running on the XGMII clock (156,25 MHz) to XGMII stream in 64bit mode (without DDR). It generates the interframe gap of minimum 12 byte times, adds the Preamble and Start of Frame Delimiter (SFD) and encodes the incoming AXI stream to the XGMII interface (64bit data, 8bit control) using the control lines and special characters according to the XGMII specification. Start of frame shall always be on Lane 0. It is instantiated on the TX side of the PCS and on the RX side of the MAC.

#### XGMII RX Interface Adapter

The XGMII RX Interface Adapter converts a XGMII stream in 64bit mode (without DDR) to a 64bit AXI stream running on the XGMII clock (156,25 MHz). It removes the Preamble and Start of Frame Delimiter (SFD) and decodes the incoming XGMII stream (64bit data, 8bit control) to the AXI stream interface using the control lines and special characters according to the XGMII specification. Start of frame shall always be on Lane 0 (or 4).

It is instantiated on the RX side of the PCS and on the TX side of the MAC.

#### 2.2.1.3 Entity Declaration

| Name                   | Dir | Туре             | Size | Description                    |

|------------------------|-----|------------------|------|--------------------------------|

|                        |     | Ports            |      |                                |

| XGMii RX Clk/Rst Input |     |                  |      |                                |

| XGMiiRxClk_ClkIn       | in  | std_logic        | 1    | RX Clock                       |

| XGMiiRxRstN_RstIn      | in  | std_logic        | 1    | Reset aligned with<br>RX Clock |

| XGMii TX Clk/Rst Input |     |                  |      |                                |

| XGMiiTxClk_ClkIn       | in  | std_logic        | 1    | TX Clock                       |

| XGMiiTxRstN_RstIn      | in  | std_logic        | 1    | Reset aligned with<br>TX Clock |

| XGMii RX Data Input    |     |                  |      |                                |

| XGMiiRxCtl_Enaln       | in  | std_logic        | 8    | RX Data valid                  |

| XGMiiRxData_DatIn      | in  | std_logic_vector | 64   | RX Data                        |

| XGMii TX Data Output   |     |                  |      |                                |

| XGMiiTxCtl_EnaOut      | out | std_logic        | 1    | TX Data valid                  |

| XGMiiTxData_DatOut     | out | std_logic_vector | 64   | TX Data                        |

| Axi Input              |     |                  |      |                                |

| AxisValid_ValIn        | in  | std_logic        | 1    | AXI Stream frame               |

| AxisReady_ValOut       | out | std_logic        | 1    | input                          |

| AxisData_DatIn         | in  | std_logic_vector | 64   |                                |

| AxisStrobe_ValIn       | in  | std_logic_vector | 8    |                                |

| AxisKeep_ValIn         | in  | std_logic_vector | 8    |                                |

| AxisLast_Valln         | in  | std_logic        | 1    |                                |

| AxisUser_DatIn         | in  | std_logic_vector | 3    |                                |

| Axi Output             |     |                  |      |                                |

| AxisValid_ValOut       | out | std_logic        | 1    | AXI Stream frame               |

| AxisReady_Valln        | in  | std_logic        | 1    | output                         |

| AxisData_DatOut        | out | std_logic_vector | 64   |                                |

| AxisStrobe_ValOut      | out | std_logic_vector | 8    | ]                              |

| AxisKeep_ValOut | out | std_logic_vector | 8 |

|-----------------|-----|------------------|---|

| AxisLast_ValOut | out | std_logic        | 1 |

| AxisUser_DatOut | out | std_logic_vector | 3 |

Table 6: MAC XGMII Adapter

| Name                   | Dir | Туре             | Size   | Description                    |

|------------------------|-----|------------------|--------|--------------------------------|

|                        |     | Ports            |        |                                |

| XGMii RX Clk/Rst Input |     |                  |        |                                |

| XGMiiRxClk_ClkIn       | in  | std_logic        | 1      | RX Clock                       |

| XGMiiRxRstN_RstIn      | in  | std_logic        | 1      | Reset aligned with<br>RX Clock |

| XGMii TX Clk/Rst Input |     |                  | *<br>• |                                |

| XGMiiTxClk_ClkIn       | in  | std_logic        | 1      | TX Clock                       |

| XGMiiTxRstN_RstIn      | in  | std_logic        | 1      | Reset aligned with<br>TX Clock |

| XGMii RX Data Output   |     |                  |        |                                |

| XGMiiRxCtl_EnaOut      | out | std_logic        | 8      | RX Data valid                  |

| XGMiiRxData_DatOut     | out | std_logic_vector | 64     | RX Data                        |

| XGMii TX Data Input    | -   |                  |        |                                |

| XGMiiTxCtl_Enaln       | in  | std_logic        | 1      | TX Data valid                  |

| XGMiiTxData_DatIn      | in  | std_logic_vector | 64     | TX Data                        |

| Axi Input              |     |                  | T      |                                |

| AxisValid_ValIn        | in  | std_logic        | 1      | AXI Stream frame               |

| AxisReady_ValOut       | out | std_logic        | 1      | input                          |

| AxisData_DatIn         | in  | std_logic_vector | 64     |                                |

| AxisStrobe_Valln       | in  | std_logic_vector | 8      |                                |

| AxisKeep_Valln         | in  | std_logic_vector | 8      | -                              |

| AxisLast_Valln         | in  | std_logic        | 1      | -                              |

| AxisUser_DatIn         | in  | std_logic_vector | 3      | -                              |

| Axi Output             |     |                  |        |                                |

| AxisValid_ValOut       | out | std_logic        | 1      | AXI Stream frame               |

| AxisReady_Valln        | in  | std_logic        | 1      | output                         |

| AxisData_DatOut        | out | std_logic_vector | 64     |                                |

| AxisStrobe_ValOut      | out | std_logic_vector | 8      | ]                              |

| AxisKeep_ValOut        | out | std_logic_vector | 8      | ]                              |

| AxisLast_ValOut        | out | std_logic        | 1      |                                |

| AxisUser_DatOut        | out | std_logic_vector | 3      | ]                              |

Table 7:PHY XGMII Adapter

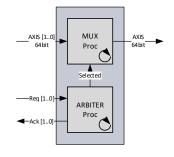

## 2.2.2 Arbiter

#### 2.2.2.1 Entity Block Diagram

Figure 5: Arbiter

## 2.2.2 Entity Description

The Arbiter was designed to have minimal delay and maximum throughput since it needs to provide valid Data at every clock cycle once started and shall not slow down the forwarding path.

In the design the Arbiter is controlled by two Forward FIFOs in Store-And-Forward mode. As soon as the FIFO has valid data available it will assert the Req line and will wait with providing data with the valid signal until the Ack is set. At the end of the frame if there is still data available in the FIFO it will assert the Req line again. This assures a zero delay switchover or when frames come back to back. The Ack signal is changing with one clock cycle delay when access is granted.

To guarantee that no path starves it switches between the paths if both of them have ready data to send, this also guarantees that the maximum delay one port has to wait until it is served again is the maximum size of one frame (if both request only when data is valid). If no path wanted to send and at the next moment both of them want to send, path 1 has priority over path 2. Back-pressure is directly forwarded to the path selected. The path not selected doesn't get the Ack line set and the AXI ready signal is low. If no path is selected (after the last frame was sent and no path has data ready to send) the Ack signals are low and the AXI ready signal to both input ports is low.

## 2.2.2.3 Entity Declaration

| XGMiiClk_ClkIn        | in    | std_logic                 | 1  | XGMII Clock             |

|-----------------------|-------|---------------------------|----|-------------------------|

| XGMiiRstN_RstIn       | in    | std_logic                 | 1  | XGMII Reset             |

| Arbiter Request Input |       |                           |    |                         |

| Req_ValIn             | in    | std_logic_vector          | 2  | Request access          |

| Arbiter Acknowledge C | utput |                           |    |                         |

| Ack_ValOut            | in    | std_logic_vector          | 2  | Acknowledge ac-<br>cess |

| Axi Input             |       |                           | r  | •                       |

| AxisValid_Valln       | in    | Axis64_Itf<br>Valid_Type  | 2  | AXI Stream frame input  |

| AxisReady_ValOut      | out   | Axis64_ltf<br>Ready_Type  | 2  |                         |

| AxisData_DatIn        | in    | Axis64_Itf<br>Data_Type   | 2  |                         |

| AxisStrobe_ValIn      | in    | Axis64_Itf<br>Strobe_Type | 2  | -                       |

| AxisKeep_ValIn        | in    | Axis64_ltf<br>Keep_Type   | 2  |                         |

| AxisLast_Valln        | in    | Axis64_Itf<br>Last_Type   | 2  |                         |

| AxisUser_DatIn        | in    | Axis64_ltf<br>User_Type   | 2  |                         |

| Axi Output            |       |                           | 1  |                         |

| AxisValid_ValOut      | out   | std_logic                 |    | AXI Stream frame        |

| AxisReady_Valln       | in    | std_logic                 | 1  | output                  |

| AxisData_DatOut       | out   | std_logic_vector          | 64 |                         |

| AxisStrobe_ValOut     | out   | std_logic_vector          | 8  |                         |

| AxisKeep_ValOut       | out   | std_logic_vector          | 8  |                         |

| AxisLast_ValOut       | out   | std_logic                 | 1  |                         |

| AxisUser_DatOut       | out   | std_logic_vector          | 3  | 1                       |

Table 8: Arbiter

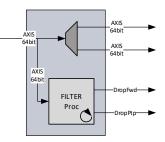

## 2.2.3 PTP Filter and Splitter

#### 2.2.3.1 Entity Block Diagram

Figure 6: PTP Filter and Splitter

#### 2.2.3.2 Entity Description

The Filter and Splitter has two functionalities: The first functionality is that it splits the AXI stream into two AXI streams and makes sure that data transfers are done when both output AXI streams are ready, even though the output AXI streams will always signal valid because the Arbiter and Splitter is connected to two Forwarding FIFOs which signal ready always.

The second functionality is that it parses the incoming frame to check if it is a PTP frame or not. The parser checks several things:

- Destination MAC for the dedicate PTP Multicast Mac Addresses

- Etherthertype dedicated to PTP if in Layer 2 mode

- Destination IP Addresses for the dedicated PTP Multicast IP Addresses and UDP Destination Ports dedicated to PTP if in Layer 3 (UDP/IPv4 or IPv6) mode

- VLAN if used, which shifts byte alignment by 4

- Redundancy Tags, which shifts byte alignment by 6

If it is a PTP frame it asserts the drop signal for the forwarding path. If it is not a PTP frame it will assert the drop signal for the PTP receive path.

The drop signal shall be asserted for a single clock cycle whenever the frame type is detected.

The parser must be able to run at full speed without the need for backpressure.

#### 2.2.3.3 Entity Declaration

| Generics | Name | Dir | Туре     | Size | Description |

|----------|------|-----|----------|------|-------------|

|          |      |     | Generics |      |             |

| UnicastProfile<br>Support_Gen-Boolean1If Unicast Frames<br>shall be handledSystem<br>S(MilCIK_CIK_nownee<br>S(MilCIK_CIK_nownee<br>Arbiter Acknowledge Outputinstd_logic1XGMIICIOckArbiter Acknowledge Outputandstd_logic_vector2Drop indication if it<br>is a PTP frame or<br>nownee do to the<br>MAC or the PTP<br>core (either or)Drop indication if it<br>is a PTP frame or<br>nownee do to the<br>MAC or the PTP<br>core (either or)Axi Inputandstd_logic_vector64AxisData_Datininstd_logic_vector84AxisStrobe_ValIninstd_logic_vector84AxisStrobe_ValIninstd_logic_vector84AxisUser_Datininstd_logic_vector84AxisValid_Valuninstd_logic_vector84AxisStast_Valininstd_logic_vector84AxisStrobe_Valininstd_logic_vector84AxisValid_Valuninstd_logic_vector84AxisValid_ValunoutAxis64_ltf<br>Ready_Type2AxisValid_ValunoutAxis64_ltf<br>Keep_Type2AxisStrobe_ValunoutAxis64_ltf<br>Keep_Type2AxisStrobe_ValoutoutAxis64_ltf<br>Keep_Type2AxisStrobe_ValoutoutAxis64_ltf<br>Keep_Type2AxisStat_ValoutoutAxis64_ltf<br>Keep_Type2AxisStat_ValoutoutAxis64_ltf<br>Keep_Type2AxisStat_ValoutoutAxis64_ltf<br>Keep_Type2 <tr< th=""><th></th><th></th><th></th><th></th><th></th></tr<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   |     |                  |   |                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----|------------------|---|-----------------------------------------------------------------------------------|

| PortsSystemXGMilClk_Clkininstd_logic1XGMil ClockXGMilRstN_Rstininstd_logic1XGMil ResetArbiter Acknowledge Output </td <td></td> <td>-</td> <td>Boolean</td> <td>1</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   | -   | Boolean          | 1 |                                                                                   |

| System<br>XGMilClk_Clkininstd_logic1XGMil ClockXGMilRstN_Rstininstd_logic1XGMil ResetArbiter Acknowledge Output </td <td></td> <td></td> <td>Douto</td> <td></td> <td>Shall be handled</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                   |     | Douto            |   | Shall be handled                                                                  |

| XGMiiClk_Clkininstd_logic1XGMii ClockXGMiiRstN_Rstininstd_logic1XGMii ResetArbiter Acknowledge OutputXGMii ResetDrop_ValOutoutstd_logic_vector2Drop indication if it is a PTP frame or not. It will either be forwarded to the MAC or the PTP core (either or)Axi InputAxisValid_ValIn1AXI Stream frameAxisQata_DatIninstd_logic_vector64AxisStobe_ValIninstd_logic_vector8AxisUser_DatIninstd_logic_vector8AxisValid_ValOutoutAxis64_ltf<br>Ready_Type2AXI Stream frame<br>outputAxisValid_ValOutoutAxis64_ltf<br>Ready_Type2AXI Stream frame<br>outputAxisValid_ValOutoutAxis64_ltf<br>Ready_Type2AXI Stream frame<br>outputAxisStrobe_ValIninstd_logic_vector3AXI Stream frame<br>outputAxisValid_ValOutoutAxis64_ltf<br>Ready_Type2AXI Stream frame<br>outputAxisStrobe_ValOutoutAxis64_ltf<br>Ready_Type2Axis64_ltf<br>Ready_Type2AxisStrobe_ValOutoutAxis64_ltf<br>Ready_Type2Axis64_ltf<br>Ready_Type2AxisLast_ValOutoutAxis64_ltf<br>Reep_Type2Axis64_ltf<br>Reep_Type2AxisLast_ValOutoutAxis64_ltf<br>Reep_Type2Axis64_ltf<br>Reep_Type2AxisLast_ValOutoutAxis6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |     | Ports            |   |                                                                                   |

| XGMIIRstN_RstIninstd_logic1XGMII ResetArbiter Acknowledge OutputDrop indication if it is a PTP frame or not. It will either be forwarded to the MAC or the PTP core (either or)Drop_ValOutoutstd_logic_vector2AXI Stream frame inputAxisValid_ValIninstd_logic_vector64AxisStrobe_ValIninstd_logic_vector8AxisStrobe_ValIninstd_logic_vector8AxisStrobe_ValIninstd_logic_vector8AxisStrobe_ValIninstd_logic_vector3AxisStast_ValIninstd_logic_vector3AxisStast_ValIninstd_logic_vector3AxisStast_ValIninstd_logic_vector3AxisStast_ValIninstd_logic_vector3AxisStast_ValInoutAxis64_ltf<br>Data_Type2AxisStaid_ValOutoutAxis64_ltf<br>Strobe_Type2AxisStrobe_ValOutoutAxis64_ltf<br>Keep_Type2AxisStrobe_ValOutoutAxis64_ltf<br>Last_Type2AxisLast_ValOutoutAxis64_ltf<br>Last_Type2AxisLast_ValOutoutAxis64_ltf<br>Last_Type2AxisLast_ValOutoutAxis64_ltf<br>Last_Type2AxisLast_ValOutoutAxis64_ltf<br>Last_Type2AxisLast_ValOutoutAxis64_ltf<br>Last_Type2AxisLast_ValOutoutAxis64_ltf<br>Last_Type2AxisLast_ValOutout<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                   | in  | std logic        | 1 | XGMII Clock                                                                       |

| Arbiter Acknowledge OutputDropUputDrop indication if it<br>is a PTP frame or<br>not. It will either be<br>forwarded to the<br>MAC or the PTP<br>core (either or)Axi Inputinstd_logic_vector2AXIS Creater or<br>not. It will either be<br>forwarded to the<br>MAC or the PTP<br>core (either or)AxisValid_ValIninstd_logic1AxisSata_Datininstd_logic_vector64AxisStrobe_ValIninstd_logic_vector8AxisStrobe_ValIninstd_logic_vector8AxisStrobe_ValIninstd_logic_vector3AxisUser_Datininstd_logic_vector3AxisOutputoutAxis64_ltf<br>Valid_Type2AxisValid_ValOutoutAxis64_ltf<br>Strobe_Type2AxisStrobe_ValOutoutAxis64_ltf<br>Strobe_Type2AxisStrobe_ValOutoutAxis64_ltf<br>Last_Type2AxisLast_ValOutoutAxis64_ltf<br>Last_Type2AxisLast_ValOutoutAxis64_ltf<br>Last_Type2AxisLast_ValOutoutAxis64_ltf<br>Last_Type2AxisLast_ValOutoutAxis64_ltf<br>Last_Type2AxisLast_ValOutoutAxis64_ltf<br>Last_Type2AxisLast_ValOutoutAxis64_ltf<br>Last_Type2AxisLast_ValOutoutAxis64_ltf<br>Last_Type2AxisLast_ValOutoutAxis64_ltf<br>Last_Type2AxisLast_ValOutoutAxis64_ltf<br>Last_Type2AxisLast_ValOut </td <td></td> <td></td> <td></td> <td>1</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |     |                  | 1 |                                                                                   |

| Drop_ValOutoutstd_logic_vector2Drop indication if it<br>is a PTP frame or<br>not. It will either be<br>forwarded to the<br>MAC or the PTP<br>core (either or)Axi Inputinstd_logic1AxisValid_ValIninstd_logic_vector1AxisReady_ValOutoutstd_logic_vector64AxisData_DatIninstd_logic_vector8AxisStrobe_ValIninstd_logic_vector8AxisStrobe_ValIninstd_logic_vector8AxisUser_DatIninstd_logic_vector8AxisUser_DatIninstd_logic_vector8AxisUser_DatIninstd_logic_vector8AxisUser_DatIninstd_logic_vector8AxisUser_DatIninstd_logic_vector8AxisUser_DatIninstd_logic_vector8AxisUser_DatIninstd_logic_vector8AxisUser_DatIninstd_logic_vector8AxisUser_DatInoutAxis64_ltf2AxisStrobe_ValOutoutAxis64_ltf2AxisStrobe_ValOutoutAxis64_ltf2AxisStrobe_ValOutoutAxis64_ltf2AxisKeep_ValOutoutAxis64_ltf2AxisLast_ValOutoutAxis64_ltf2AxisLast_ValOutoutAxis64_ltf2AxisLast_ValOutoutAxis64_ltf2AxisLast_ValOutoutAxis64_ltf2AxisLast_ValOutoutAxis64_ltf <td< td=""><td></td><td></td><td>stu_logic</td><td></td><td>XOMII Keset</td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                   |     | stu_logic        |   | XOMII Keset                                                                       |

| AxisValid_Vallninstd_logic1AXI Stream frame<br>inputAxisReady_ValOutoutstd_logic_vector64AxisData_Datininstd_logic_vector8AxisStrobe_Vallninstd_logic_vector8AxisLast_Vallninstd_logic_vector8AxisUser_Datininstd_logic_vector8AxisUser_Datininstd_logic_vector3AxisUser_Datininstd_logic_vector3AxisUser_Datininstd_logic_vector3AxisUser_Datininstd_logic_vector3AxisUser_DatinoutAxis64_ltf<br>Paid_Type2AxisCalld_ValOutoutAxis64_ltf<br>Data_Type2AxisData_DatOutoutAxis64_ltf<br>Data_Type2AxisStrobe_ValOutoutAxis64_ltf<br>Keep_Type2AxisLast_ValOutoutAxis64_ltf<br>Las_Type2AxisLast_ValOutoutAxis64_ltf<br>Las_Type2AxisLast_ValOutoutAxis64_ltf<br>Las_Type2AxisLast_ValOutoutAxis64_ltf<br>Las_Type2AxisLast_ValOutoutAxis64_ltf<br>Las_Type2AxisLast_ValOutoutAxis64_ltf<br>Las_Type2AxisLast_ValOutoutAxis64_ltf<br>Las_Type2AxisLast_ValOutoutAxis64_ltf<br>Las_Type2AxisLast_ValOutoutAxis64_ltf<br>Las_Type2AxisLast_ValOutoutAxis64_ltf<br>Las_Type2 <td>Drop_ValOut</td> <td></td> <td>std_logic_vector</td> <td>2</td> <td>is a PTP frame or<br/>not. It will either be<br/>forwarded to the<br/>MAC or the PTP</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Drop_ValOut       |     | std_logic_vector | 2 | is a PTP frame or<br>not. It will either be<br>forwarded to the<br>MAC or the PTP |

| Axis Valid_ValinAxis EncloseImage: Constraint of the point of  |                   |     |                  | 1 |                                                                                   |

| AxisData_Datininstd_logic_vector64AxisData_Datininstd_logic_vector8AxisStrobe_Valininstd_logic_vector8AxisLast_Valininstd_logic_vector8AxisUser_Datininstd_logic_vector3AxiOutputAxis64_ltf2AxisValid_ValOutoutAxis64_ltf2AxisReady_ValininAxis64_ltf2AxisData_DatOutoutAxis64_ltf2AxisStrobe_ValOutoutAxis64_ltf2AxisStrobe_ValOutoutAxis64_ltf2AxisKeep_ValOutoutAxis64_ltf2AxisKeep_ValOutoutAxis64_ltf2AxisLast_ValOutoutAxis64_ltf2AxisKeep_ValOutoutAxis64_ltf2AxisLast_ValOutoutAxis64_ltf2AxisLast_ValOutoutAxis64_ltf2AxisLast_ValOutoutAxis64_ltf2AxisLast_ValOutoutAxis64_ltf2AxisLast_ValOutoutAxis64_ltf2AxisLast_ValOutoutAxis64_ltf2AxisLast_ValOutoutAxis64_ltf2AxisLast_ValOutoutAxis64_ltf2AxisLast_ValOutoutAxis64_ltf2AxisLast_ValOutoutAxis64_ltf2AxisLast_ValOutoutAxis64_ltf2AxisLast_ValOutoutAxis64_ltf2AxisLast_ValOut <td< td=""><td>AxisValid_ValIn</td><td></td><td></td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | AxisValid_ValIn   |     |                  |   |                                                                                   |

| AxisStrobe_Vallninstd_logic_vector8AxisStrobe_Vallninstd_logic_vector8AxisLast_Vallninstd_logic_vector8AxisUser_Datlninstd_logic_vector3AxiOutputinstd_logic_vector3AxisValid_ValOutoutAxis64_ltf<br>Valid_Type2AxisReady_VallninAxis64_ltf<br>Ready_Type2AxisData_DatOutoutAxis64_ltf<br>Data_Type2AxisStrobe_ValOutoutAxis64_ltf<br>Strobe_Type2AxisKeep_ValOutoutAxis64_ltf<br>Last_Type2AxisLast_ValOutoutAxis64_ltf<br>Last_Type2AxisLast_ValOutoutAxis64_ltf<br>Last_Type2AxisLast_ValOutoutAxis64_ltf<br>Last_Type2AxisLast_ValOutoutAxis64_ltf<br>Last_Type2AxisLast_ValOutoutAxis64_ltf<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | AxisReady_ValOut  |     |                  | • | input                                                                             |

| AxisConcest_runninstd_logic_vector8AxisKeep_Vallninstd_logic1AxisLast_Vallninstd_logic_vector3AxisUser_DatIninstd_logic_vector3Axi OutputoutAxis64_ltf<br>Valid_Type2AXI Stream frame<br>outputAxisValid_ValOutoutAxis64_ltf<br>Ready_Type2AXI Stream frame<br>outputAxisReady_ValIninAxis64_ltf<br>Data_Type2AXI Stream frame<br>outputAxisData_DatOutoutAxis64_ltf<br>Data_Type22AxisStrobe_ValOutoutAxis64_ltf<br>Keep_Type2AxisKeep_ValOutoutAxis64_ltf<br>Last_Type2AxisLast_ValOutoutAxis64_ltf<br>Last_Type2Axislater_DatOutoutAxis64_ltf<br>Last_Type2AxisLast_ValOutoutAxis64_ltf<br>Last_Type2Axislater_DatOutoutAxis64_ltf<br>Last_Type2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | AxisData_DatIn    | in  |                  |   |                                                                                   |

| AxisUser_Vallninstd_logic1AxisUser_Datlninstd_logic_vector3AxioUtputinstd_logic_vector3AxioUtputoutAxis64_ltf<br>Valid_Type2AxisReady_VallninAxis64_ltf<br>Ready_Type2AxisData_DatOutoutAxis64_ltf<br>Data_Type2AxisStrobe_ValOutoutAxis64_ltf<br>Data_Type2AxisKeep_ValOutoutAxis64_ltf<br>Strobe_Type2AxisKeep_ValOutoutAxis64_ltf<br>Last_Type2AxisLast_ValOutoutAxis64_ltf<br>Last_Type2AxisLast_ValOutoutAxis64_ltf<br>Last_Type2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | AxisStrobe_ValIn  | in  | std_logic_vector | 8 |                                                                                   |

| AxisUser_DatininStd_logic_vector3AxisUser_Datininstd_logic_vector3Axi OutputoutAxis64_ltf2AxisValid_ValOutoutAxis64_ltf2AxisReady_ValininAxis64_ltf2AxisData_DatOutoutAxis64_ltf2AxisStrobe_ValOutoutAxis64_ltf2AxisStrobe_ValOutoutAxis64_ltf2AxisKeep_ValOutoutAxis64_ltf2AxisKeep_ValOutoutAxis64_ltf2AxisLast_ValOutoutAxis64_ltf2AxisLast_ValOutoutAxis64_ltf2AxisLast_ValOutoutAxis64_ltf2AxisLast_ValOutoutAxis64_ltf2AxisLast_ValOutoutAxis64_ltf2AxisLast_ValOutoutAxis64_ltf2AxisLast_ValOutoutAxis64_ltf2AxisLast_ValOutoutAxis64_ltf2AxisLast_ValOutoutAxis64_ltf2AxisLast_ValOutoutAxis64_ltf2AxisLast_ValOutoutAxis64_ltf2AxisLast_ValOutoutAxis64_ltf2AxisLast_ValOutoutAxis64_ltf2AxisLast_ValOutoutAxis64_ltf2AxisLast_ValOutoutAxis64_ltf2AxisLast_ValOutoutAxis64_ltf2AxisLast_ValOutoutAxis64_ltf2AxisLast_ValOuto                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | AxisKeep_Valln    | in  | std_logic_vector | 8 |                                                                                   |