|

Ptp_HybridClock_Flyer.pdf Size : 169.67 Kb Type : pdf |

|

Ptp_HybridClock_ReferenceManual.pdf Size : 2892.083 Kb Type : pdf |

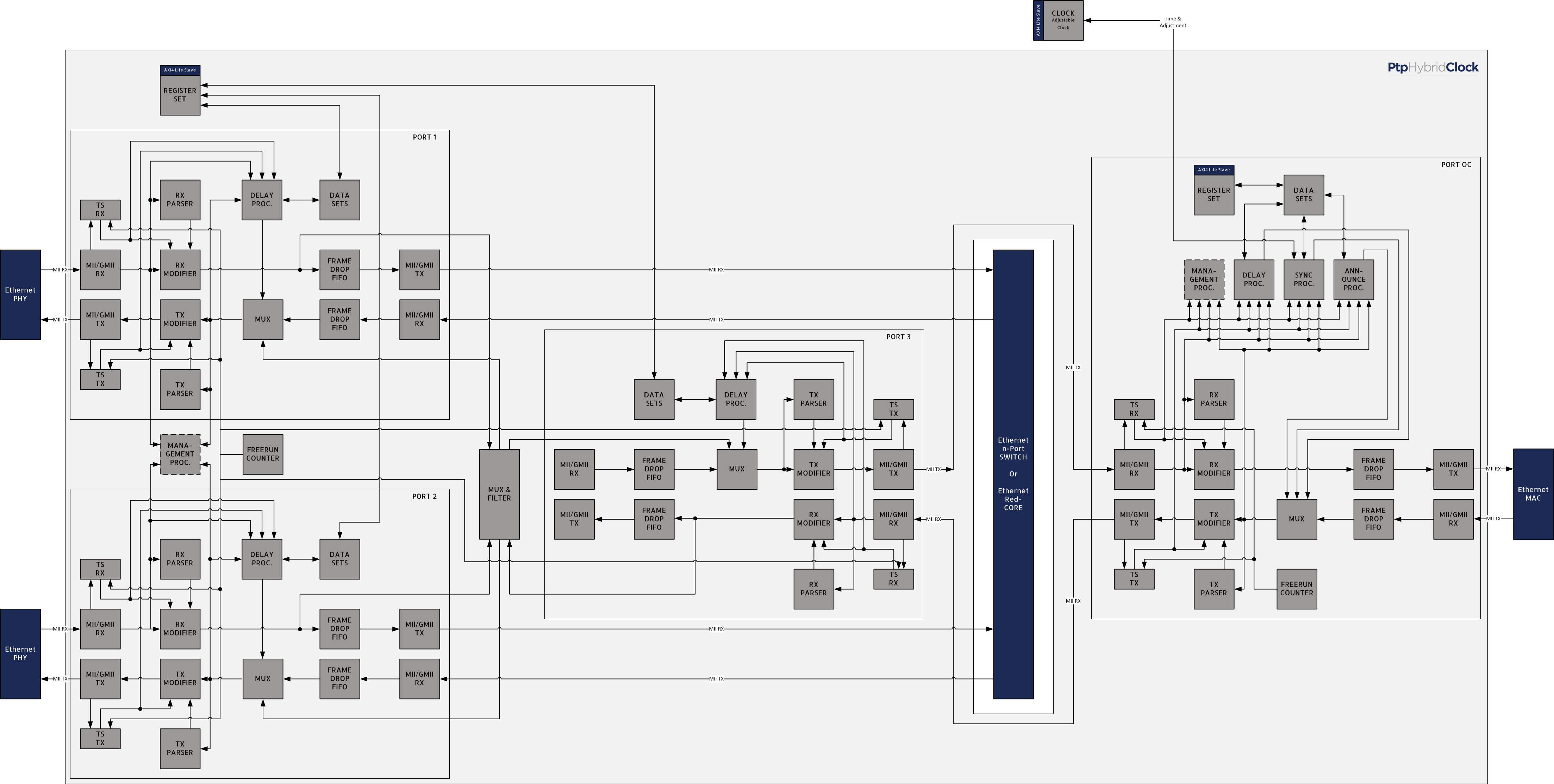

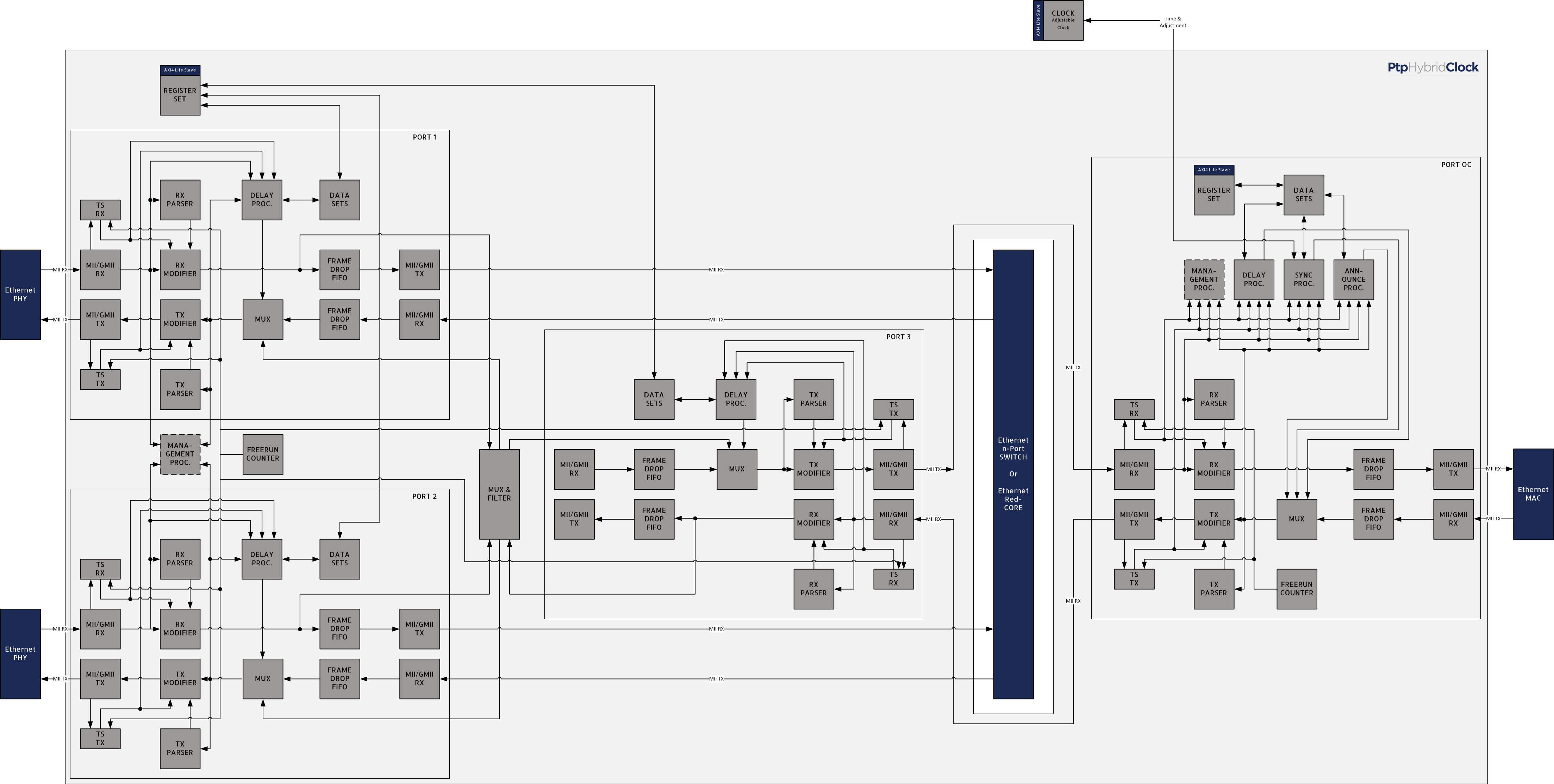

The PTP Hybrid Clock (HC) from NetTimeLogic is a combination of NetTimeLogic's PTP Transparent Clock (TC) and PTP Ordinary Clock (OC). It adds the Sync and Announce message processors to the design which allow synchronization of the clock according to IEEE1588 while keeping the timing aware frame forwarding feature of the TC. The OC will run in Slave or Master mode according to the configuration and Best-Master-Clock (BMC) algorithm. For resource optimization the OC can also be implemented as Slave-Only clock.

The HC is intercepting the path between an Ethernet PHY and an Ethernet core that forwards or handles Ethernet frames. Mostly this is used in daisy-chained networks. This allows message injection in parallel to data transfers from/to the Switching Core.

All datasets and algorithms are implemented completely in HW.

There are different licensing possibilities (more info here). All prices are in US Dollars without VAT, all prices are one-time fees, no royalties apply

All prices are non-binding estimates – please use the contact form for definitive pricing and lead-time information.

Evaluation binaries available for Terasic's SoCKit development boards or as Modelsim(R) precompiled libraries => contact us for free access

|

Ptp_HybridClock_Flyer.pdf Size : 169.67 Kb Type : pdf |

|

Ptp_HybridClock_ReferenceManual.pdf Size : 2892.083 Kb Type : pdf |