# **Ptp**HybridClock

A low-footprint, highly configurable, 100% hardware only IEEE1588-2019/2008 Hybrid Clock (Based on NetTimeLogic's TC & OC) solution, specifically designed for high-performance distributed systems. Allows running PTP synchronization completely independent and standalone from the user application especially in daisy chained networks.

#### Key Features:

- IEEE1588-2019/2008 Hybrid Clock

- 100% hardware only solution

- Vendor independent

- Layer 2 and Ipv4&6, P2P/E2E delay mechanism, 1 step clock

- Default-, Power-, Utility-, TSN-, and ITU-profile support

## Typical Applications:

- Ethernet based automation networks

- Robot control

- Substation automation

- Distributed data acquisition

- Test and measurement

- Etc.

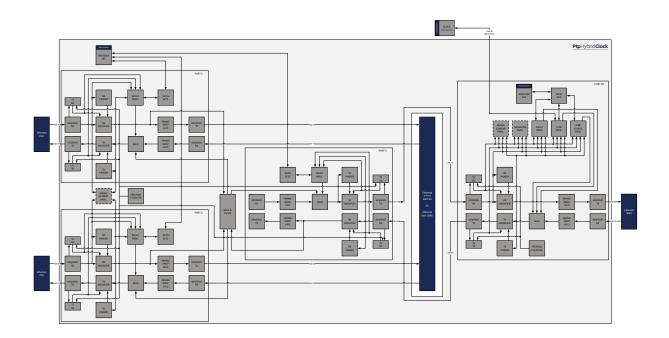

## IP Core Architecture:

Specification:

IEEE1588 Layer 2 and Ipv4, P2P/E2E delay mechanism, 1 step hybrid clock,

Master and Slave capability, multicast and unicast

2 port daisy chain, OC is able to send and receive from both ports, built out of a combination of NetTimeLogic's OC and TC

Default-, Power-, Utility-, TSN- and ITU-profile support

Complete Dataset support

PTP Management message support

Offset and drift calculation for adjusting the clock

Performance Full line speed frame handling, offloading synchronization

10/100/1000 Mbit/s support, intercepts (R)(G)MII interfaces

between MAC and PHY or an Ethernet Switch (no MAC required)

Portability 100% hardware only solution, no dependency on external CPU or

PHY features

Vendor independent, written in plain VHDL Low footprint and low frequency requirements

Accuracy Sub microsecond synchronization

With 50ppm Oscillator: +/- 100ns

Modularity Modular system; adjustable clock is a separate core

Slim and standardized interfaces are used, scalable to more ports

Configuration No CPU required, standalone configuration with signals

Axi4 lite slave support, for status and configuration

#### Deliverables:

Ip core in plain VHDL

Testbench in plain VHDL

Reference Design with 2 ports for daisy chaining

o Top level VHDL file

o Timing Constraint SDC files

o Vivado/Quartus Project file

#### **Related Products:**

PTP Ordinary Clock

PTP Transparent Clock

• PTP Grandmaster Clock

PPS Master/Slave

IRIG Master/Slave

Adjustable Clock

Signal Timestamper

Signal Generator

NetTimeLogic GmbH Synchronization Solutions Strassburgstrasse 10 8004 Zürich Switzerland contact@nettimelogic.com

Tel. +41796716211

www.nettimelogic.com