|

Pps_ClkToPps_Flyer.pdf Size : 144.486 Kb Type : pdf |

|

Pps_ClkToPps_ReferenceManual.pdf Size : 596.556 Kb Type : pdf |

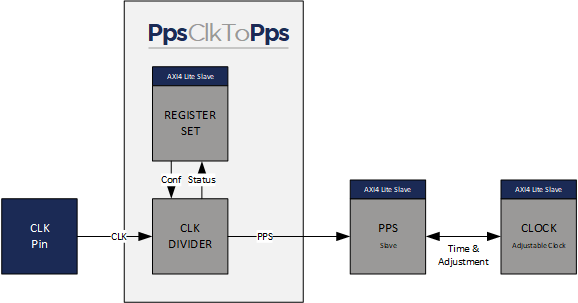

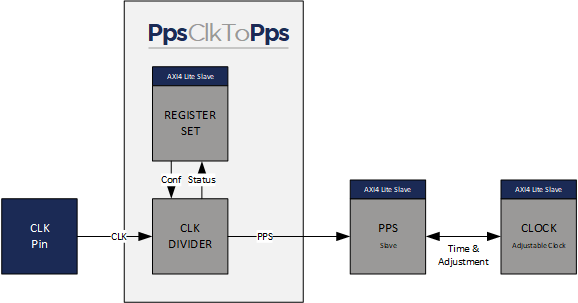

NetTimeLogic’s PPS Clock to PPS core is a full hardware (FPGA) only implementation of a PPS generator out of a clock of configurable frequency, it is intended to be connected to a PPS Slave core able to syntonize to a Pulse per Second. The core also checks if the input clock is in the configured range and only if so will generate a PPS. The core can be configured either by signals or by an AXI4Lite-Slave Register interface.

This core is intended to be used with either external clocks or also SyncE clocks when the frequency shall be adjusted numerically rather than a clock switch.

There are different licensing possibilities (more info here). All prices are in US Dollars without VAT, all prices are one-time fees, no royalties apply:

All prices are non-binding estimates – please use the contact form for definitive pricing and lead-time information.

Evaluation binaries available for the Digilent's Arty development board or as Modelsim(R) precompiled libraries => contact us for free access

|

Pps_ClkToPps_Flyer.pdf Size : 144.486 Kb Type : pdf |

|

Pps_ClkToPps_ReferenceManual.pdf Size : 596.556 Kb Type : pdf |