|

Dcf_Slave_Flyer.pdf Size : 151.467 Kb Type : pdf |

|

Dcf_Slave_ReferenceManual.pdf Size : 711.155 Kb Type : pdf |

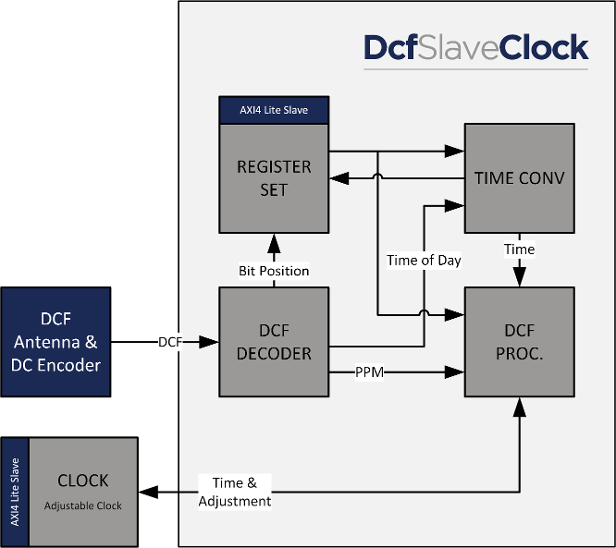

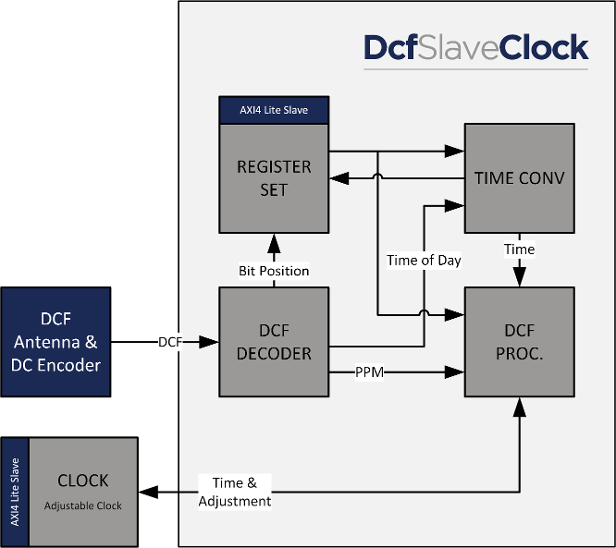

NetTimeLogic’s DCF Slave Clock is a full hardware (FPGA) only implementation of a synchronization core able to synchronize to a DCF signal encoded as PWM. The encoding scheme is the one of the DCF77 sender near Frankfurt, Germany. The whole encoding, algorithms and calculations are implemented in the core, no CPU is required. This allows running DCF77 synchronization completely independent and standalone from the user application. The core can be configured either by signals or by an AXI4Light-Slave Register interface.

All calculations and corrections are implemented completely in HW.

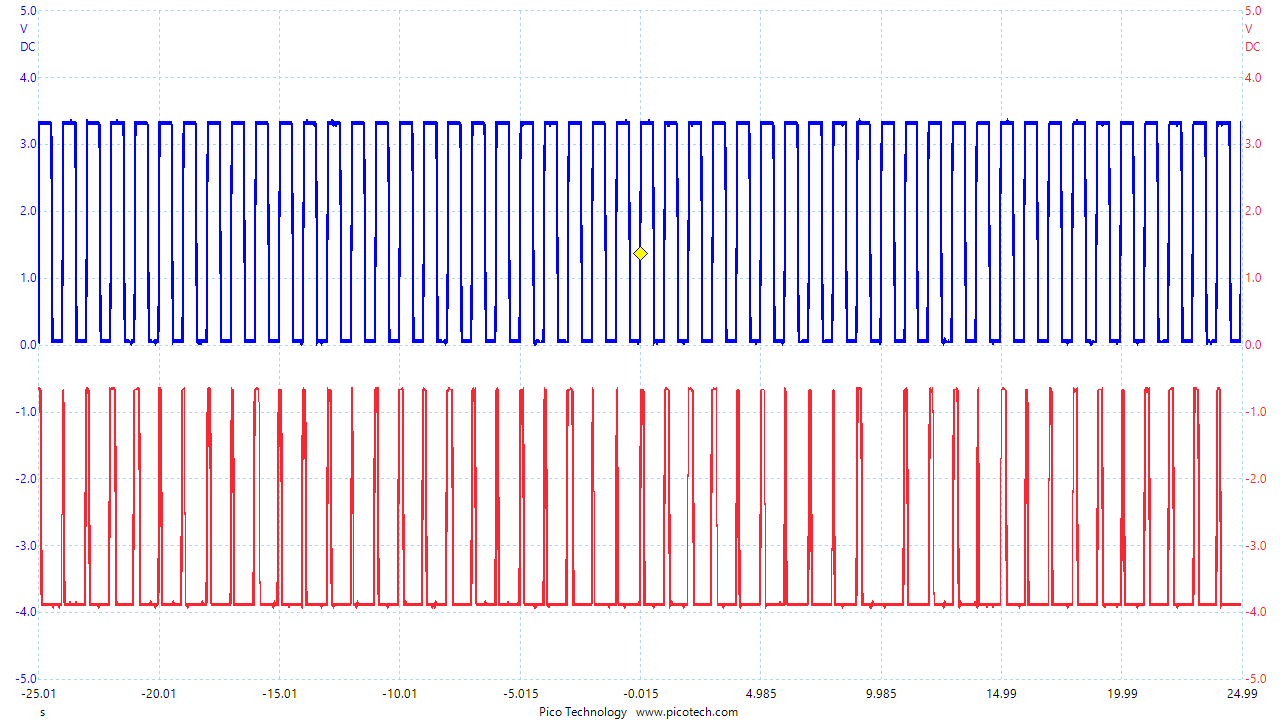

The DCF Slave Clock requires a PWM encoded DCF77 signal (see picture on the right), this can be purchased for under 20$ at e.g. Conrad

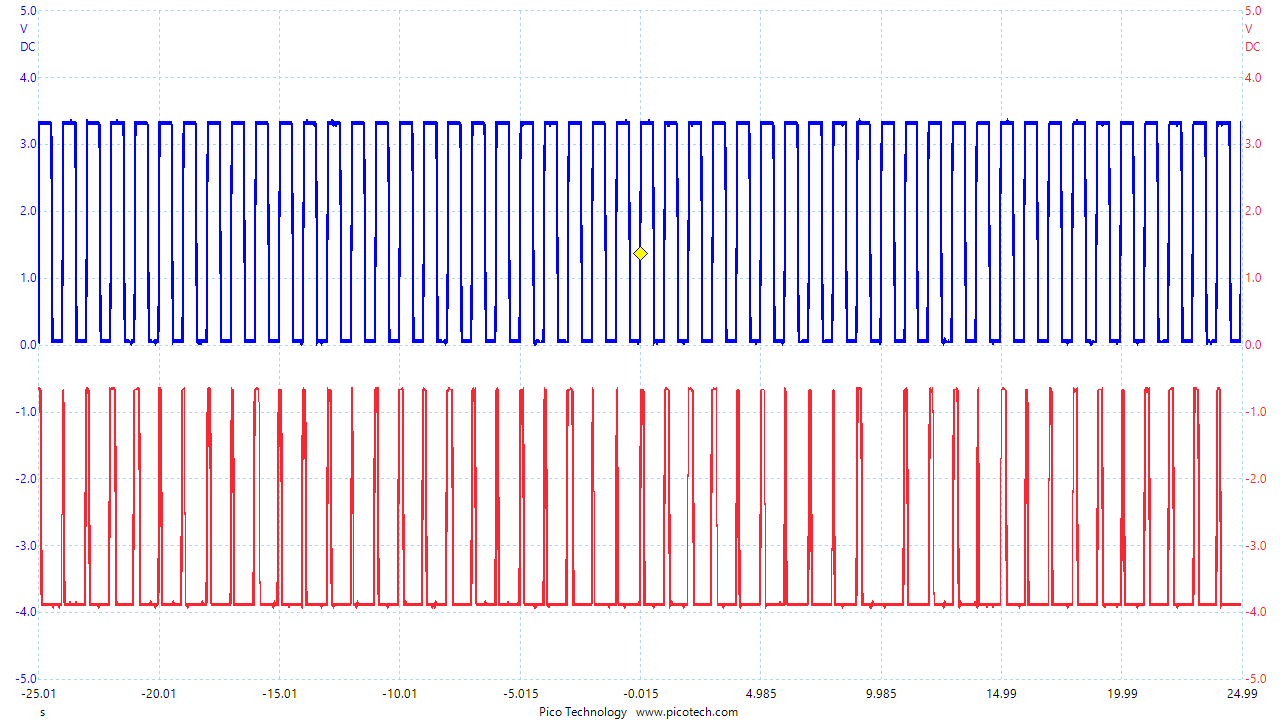

Data Stream from DCF antenna with encoder aligned with synchronized PPS

There are different licensing possibilities (more info here). All prices are in US Dollars without VAT, all prices are one-time fees, no royalties apply:

All prices are non-binding estimates – please use the contact form for definitive pricing and lead-time information.

Evaluation binaries available for Digilent's Arty and Terasic's SoCKit development boards or as Modelsim(R) precompiled libraries => contact us for free access

|

Dcf_Slave_Flyer.pdf Size : 151.467 Kb Type : pdf |

|

Dcf_Slave_ReferenceManual.pdf Size : 711.155 Kb Type : pdf |