|

Clk_SignalTimestamper_Flyer.pdf Size : 150.572 Kb Type : pdf |

|

Clk_SignalTimestamper_ReferenceManual.pdf Size : 810.691 Kb Type : pdf |

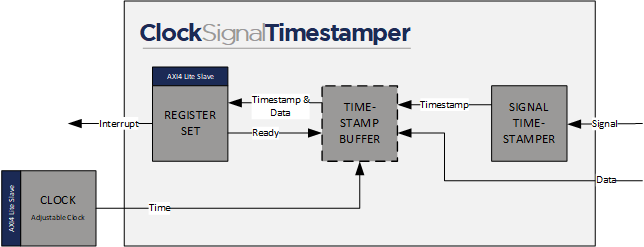

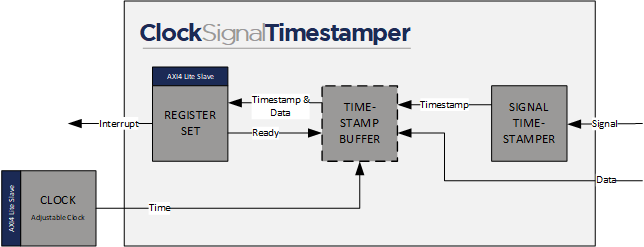

The Signal Timestamper from NetTimeLogic is a timestamper with nanosecond resolution (second and nanosecond format). It uses NetTimeLogic's Adjustable Clock core as source for timestamping. Together with the event to timestamp, data can be provided which will then be latched, so that the timestamp and data can be aligned with each other. Timestamps will generate an IRQ and timestamps can optionally be buffered for burst handling.

The IP core comes with a Linux Driver

There are different licensing possibilities (more info here). All prices are in US Dollars without VAT, all prices are one-time fees, no royalties apply:

All prices are non-binding estimates – please use the contact form for definitive pricing and lead-time information.

Evaluation binaries available for Digilent's Arty and Terasic's SoCKit development boards or as Modelsim(R) precompiled libraries => contact us for free access

|

Clk_SignalTimestamper_Flyer.pdf Size : 150.572 Kb Type : pdf |

|

Clk_SignalTimestamper_ReferenceManual.pdf Size : 810.691 Kb Type : pdf |