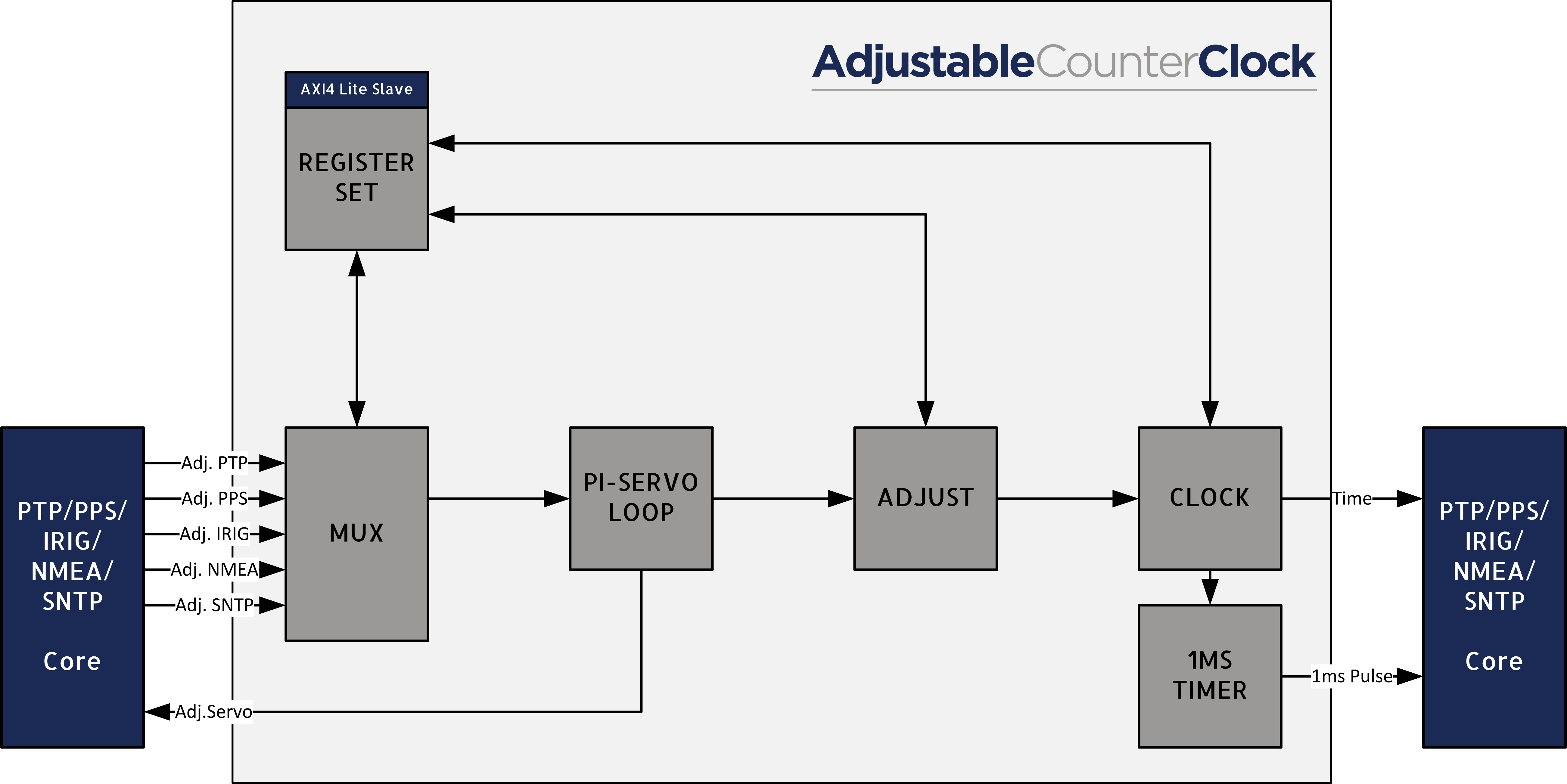

The Adjustable Clock from NetTimeLogic is an adjustable counter clock with nanosecond resolution (second and nanosecond format). It is used by all other cores from NetTimeLogic but can also be used as standalone core. It contains a hardware implemented PI servo loop (which also can be bypassed) for smooth adjustment of drift and offset. Drift and Offset correction are adjusted in parallel and individual. It can take any input frequency, even with non-integer clock periods (e.g. 66MHz) which is handled with fractional subcounters. It has multiple adjustment inputs which are multiplexed to define the source of synchronization.

An optional add-on core allows to also adjust the frequency directly on a SiTime oscillator via I2C.

All calculations and corrections are implemented completely in HW.

The IP core comes with a Linux Driver

There are different licensing possibilities (more info here). All prices are in US Dollars without VAT, all prices are one-time fees, no royalties apply:

All prices are non-binding estimates – please use the contact form for definitive pricing and lead-time information.