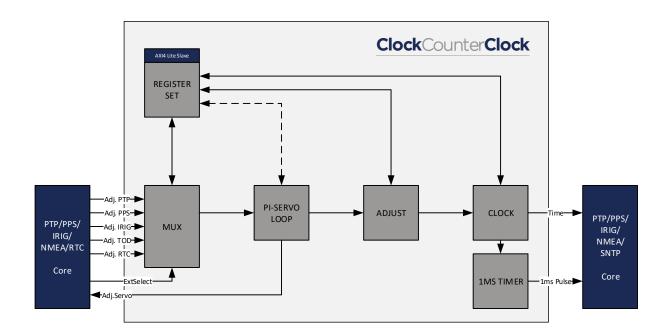

# **Clock**Counter**Clock**

A low-footprint, highly configurable, 100% hardware only Adjustable Counter Clock solution, with nanosecond resolution (second, nanosecond format). Used by all other cores from NetTimeLogic but can also run as standalone core. Generates 1ms timer events aligned with the clock (phase and frequency).

#### Key Features:

- Adjustable Counter Clock

- Hardware PI servo loops

- Any input frequency, fractional counters

- Multiplexing of adjustment sources

- 1ms timer aligned with clock

- Advanced Holdover

- Outlier Filter

## Typical Applications:

- Ethernet based automation networks

- Robot control

- Substation automation

- Distributed data acquisition

- Test and measurement

- PWM generation

## IP Core Architecture:

| Specification: |                                                                  |

|----------------|------------------------------------------------------------------|

| Counter        | 32bit nanosecond, 32bit second counter                           |

|                | Fractional counter for non-integer frequencies                   |

|                | Individual Drift and Offset correction                           |

|                | Max. drift +/- 1ns per clock cycle                               |

|                | Max. offset +/- 1 clock period per clock cycle                   |

|                | Hardware PI servo loops, individual P and I for Drift and Offset |

|                | changeable at runtime, Advance Holdover and Outlier Filter       |

| Performance    | High performance PI servo loop calculation with supervision      |

|                | 1ms timer events aligned with the clock counter (phase and       |

|                | frequency)                                                       |

| Portability    | 100% hardware only solution, no dependency on external CPU       |

|                | Vendor independent, written in plain VHDL                        |

|                | Low footprint and low frequency requirements                     |

| Accuracy       | Nanosecond resolution with sub-nanosecond fractional counter     |

|                | for even spreading of non-integer frequencies.                   |

| Modularity     | Used by all other cores from NetTimeLogic                        |

|                | Multiple ajustement inputs (PTP, PPS, IRIG, etc.)                |

|                | Slim interfaces to other cores                                   |

| Configuration  | No CPU required, standalone configuration with signals           |

|                | Axi4 lite slave support, for status and configuration            |

## Deliverables:

- Ip core in plain VHDL

- Testbench in plain VHDL

- Reference Design

- o Top level VHDL file

- o Timing Constraint SDC files

- o Vivado/Quartus Project file

- Linux Driver (PHC)

## Related Products:

- PTP Ordinary Clock

- PTP Transparent Clock

- PTP Grandmaster Clock

- PTP Hybrid Clock

- PPS Master/Slave

- IRIG Master/Slave

- Signal Timestamper

- Signal Generator

**NetTimeLogic GmbH** Synchronization Solutions Strassburgstrasse 10 8004 Zürich Switzerland contact@nettimelogic.com Tel. +41796716211 www.nettimelogic.com

Information contained in this product brief is subject to change without notice. Trademarks used are property of their respective owners. Copyright © 2025 NetTimeLogic GmbH. All rights reserved.