# **Tsn**Plugfest**App**

Reference Manual

| Product Info    |            |

|-----------------|------------|

| Product Manager | Sven Meier |

| Author(s)       | Sven Meier |

| Reviewer(s)     | -          |

| Version         | 1.1        |

| Date            | 20.06.2019 |

# **Copyright Notice**

Copyright © 2025 NetTimeLogic GmbH, Switzerland. All rights reserved. Unauthorized duplication of this document, in whole or in part, by any means, is prohibited without the prior written permission of NetTimeLogic GmbH, Switzerland.

All referenced registered marks and trademarks are the property of their respective owners

# Disclaimer

The information available to you in this document/code may contain errors and is subject to periods of interruption. While NetTimeLogic GmbH does its best to maintain the information it offers in the document/code, it cannot be held responsible for any errors, defects, lost profits, or other consequential damages arising from the use of this document/code.

NETTIMELOGIC GMBH PROVIDES THE INFORMATION, SERVICES AND PROD-UCTS AVAILABLE IN THIS DOCUMENT/CODE "AS IS," WITH NO WARRANTIES WHATSOEVER. ALL EXPRESS WARRANTIES AND ALL IMPLIED WARRANTIES, INCLUDING WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTIC-ULAR PURPOSE, AND NON-INFRINGEMENT OF PROPRIETARY RIGHTS ARE HEREBY DISCLAIMED TO THE FULLEST EXTENT PERMITTED BY LAW. IN NO EVENT SHALL NETTIMELOGIC GMBH BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, CONSEQUENTIAL, SPECIAL AND EXEMPLARY DAMAGES, OR ANY DAMAGES WHATSOEVER, ARISING FROM THE USE OR PERFORMANCE OF THIS DOCUMENT/CODE OR FROM ANY INFORMATION, SERVICES OR PRODUCTS PROVIDED THROUGH THIS DOCUMENT/CODE, EVEN IF NETTIMELOGIC GMBH HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

IF YOU ARE DISSATISFIED WITH THIS DOCUMENT/CODE, OR ANY PORTION THEREOF, YOUR EXCLUSIVE REMEDY SHALL BE TO CEASE USING THE DOCU-MENT/CODE.

# Overview

NetTimeLogic's TSN Plugfest Application core is a full hardware (FPGA) only implementation of the IIC Plugfest Interoperability Application. It implements the Real-time Data Transmission (Talker), Real-time Data Reception (Listener), Analysis Application and Analysis Result Publication (Analyzer) according to the "IIC Interoperability Application v0.3" specification.

It also contains a LED Pattern Generator and a LED Application which generates the PWM brightness pattern as described in the "LED Strip Demo Application v0.3" specification.

In addition it allows to connect an external data sink and source which can receive or transmit real time data which is encapsulated in the IIC Plugfest frame (which is an OPC UA raw binary frame).

The core is meant to be connected to the TSN and Adjustable Counter Clock IP Cores from NetTimeLogic.

For maximum accuracy, the core is using additional Timestampers which are directly connected to the (R)(G)MII Interface Adapters to take timestamps as close to the cable as possible.

The core can be configured either by an AXI4Lite-Slave Register interface.

# Key Features:

- Real-time Data Transmission (Talker)

- Real-time Data Reception (Listener)

- Analysis Application and Analysis Result Publication (Analyzer)

- LED Pattern Generator

- LED Application

- External Data Source interface

- External Data Sink interface

- HW Timestamping

- Which Features shall be available can be defined via Generics

- AXI4Lite register set

- Timestamp resolution with 50 MHz system clock: 10ns

# **Revision History**

This table shows the revision history of this document.

| Version | Date       | Revision                                          |

|---------|------------|---------------------------------------------------|

| 0.1     | 26.04.2019 | First draft                                       |

| 1.0     | 29.04.2019 | First release                                     |

| 1.1     | 20.06.2019 | Added Register descriptions and some minor clean- |

| 1.1     | 20.00.2013 | up                                                |

Table 1: Revision History

# Content

| 1 INTRODUCTION                                | 8       |

|-----------------------------------------------|---------|

| 1.1 Context Overview                          | 8       |

| 1.2 Function                                  | 9       |

| 1.3 Architecture                              | 9       |

| 2 TSN PLUGFEST APP BASICS                     | 12      |

| 2.1 Concept                                   | 12      |

| 2.1.1 Core Application                        | 13      |

| 2.1.2 LED Application                         | 14      |

| 2.1.3 Custom Application                      | 14      |

| 3 REGISTER SET                                | 16      |

| 3.1 Register Overview                         | 16      |

| 3.2 Register Descriptions                     | 18      |

| 3.2.1 General                                 | 18      |

| 3.2.2 Talker                                  | 23      |

| 3.2.3 Listener                                | 34      |

| 3.2.4 Analyzer                                | 37      |

| 3.2.5 LED App                                 | 41      |

| 4 DESIGN DESCRIPTION                          | 44      |

| 4.1 Interface Definition for a Custom Applica | tion 44 |

| 4.1.1 Custom Application Data Source Inter    | face 44 |

| 4.1.2 Custom Application Data Sink Interfac   | e 45    |

| 4.1.3 Interface Modes                         | 47      |

| 4.2 Top Level - TSN Plugfest App              | 48      |

| 4.3 Design Parts                              | 72      |

| 4.3.1 Talker                                  | 72      |

| 4.3.2 Listener                                | 75      |

| 4.3.3 Analyzer                                | 78      |

| 4.3 | 3.4 App LED                | 82  |

|-----|----------------------------|-----|

| 4.3 | 3.5 App LED Gen            | 84  |

| 4.3 | 5.6 Timestamper            | 86  |

| 4.3 | 5.7 Timestamp Merger       | 89  |

| 4.3 | 5.8 Registerset            | 91  |

| 4.4 | Configuration example      | 94  |

| 4.4 | I.1 AXI Configuration      | 94  |

| 4.5 | Clocking and Reset Concept | 96  |

| 4.5 | 5.1 Clocking               | 96  |

| 4.5 | 5.2 Reset                  | 96  |

| -   |                            | 07  |

| 5   | RESOURCE USAGE             | 97  |

| 5.1 | AMD/Xilinx (Kintex 7)      | 97  |

| 6   | DELIVERY STRUCTURE         | 98  |

| 7   | TESTBENCH                  | 99  |

| 1   | TESTBENCH                  | 55  |

| 7.1 | Run Testbench              | 100 |

| 8   | REFERENCE DESIGNS          | 101 |

# Definitions

| Definitions      |                                                                                                 |

|------------------|-------------------------------------------------------------------------------------------------|

| TSN Plugfest App | A defined Application for the IIC TSN Plugfest                                                  |

| Talker           | A block that can send OPC/UA frames                                                             |

| Listener         | A block that can receive OPC/UA frames                                                          |

| Analyzer         | A block which analyses the received OPC/UA frames, does statistics and publishes the statistics |

Table 2: Definitions

## Abbreviations

| Abbreviations |                                                |

|---------------|------------------------------------------------|

| AXI           | AMBA4 Specification (Stream and Memory Mapped) |

| FPGA          | Field Programmable Gate Array                  |

| IIC           | Industrial Internet Consortium                 |

| TSN           | Time Sensitive Networking                      |

| IRQ           | Interrupt, Signaling to e.g. a CPU             |

| TS            | Timestamp                                      |

| ТВ            | Testbench                                      |

| LUT           | Look Up Table                                  |

| FF            | Flip Flop                                      |

| RAM           | Random Access Memory                           |

| ROM           | Read Only Memory                               |

| VHDL          | Hardware description Language for FPGA's       |

Table 3: Abbreviations

## 1 Introduction

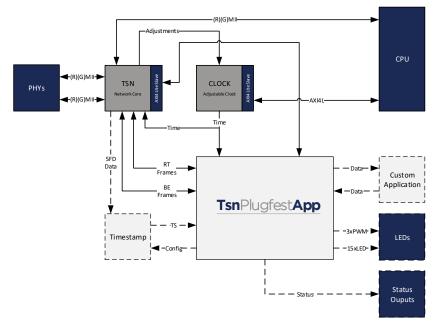

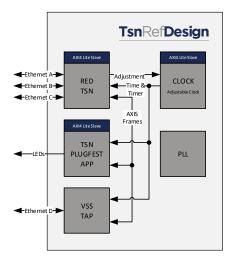

## 1.1 Context Overview

The TSN Plugfest App is meant as a co-processor handling special OPC/UA frames as defined for the IIC TSN Plugfest. It takes the time form the Adjustable Counter Clock (which is synchronized by the TSN Network Core) and generates periodic OPC/UA Real-time frames containing either a Register Value, a LED Pattern, or Custom Data encapsulated in this specific frame. For Custom Applications an interface exists which allows to send and receive data via the OPC/UA Real-time frames but without the need of handling the actual frames.

It also receives and parses the received OPC/UA Real-time frames and does statistics on the received data which is periodical published via an OPC/UA Best-effort frame. Since the OPC/UA Realtime frames contain precise timestamps a special Timestamper module is used which timestamps the frames as close as possible at the PHYs (on transmission and reception).

In addition, the core encapsulated the LED App which listens for specific Data and converts the Data in 3 PWM brightness LED outputs and provides 15 binary LED outputs which represent a light curtain as defined in the specification. It can also generate its own LED pattern, for this an LED pattern generator is implemented. All features can be enabled and disabled at synthesis time.

It contains an AXI4Lite slave for configuration and status supervision from a CPU. Additional Status signals are provided for debugging.

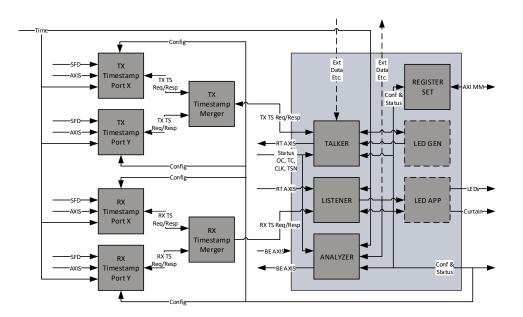

#### Figure 1: Context Block Diagram

## 1.2 Function

The TSN Plugfest App sends periodically OPC/UA Real-time frames for testing and measuring the timely behavior of the TSN core itself. The frames are sent as Layer2 multicast frames with different payload data (LED patter, Register Values, Custom App). At the same time, it is receiving the OPC/UA Real-time frames of all nodes, parses and extracts meta data, passes data to the Applications (LED PWM, Custom App) and does timely analysis (delays, offsets, etc.). The analysis result is published periodically via a OPC/UA Best-effort frames so a central node can do the analysis of the whole network.

Since for the analysis precise Timestampers are needed they are connected as close to the PHYs as possible an provide the timestamps to the Talker and Listener part.

All timestamps, scheduling etc. are based on the synchronized Clock.

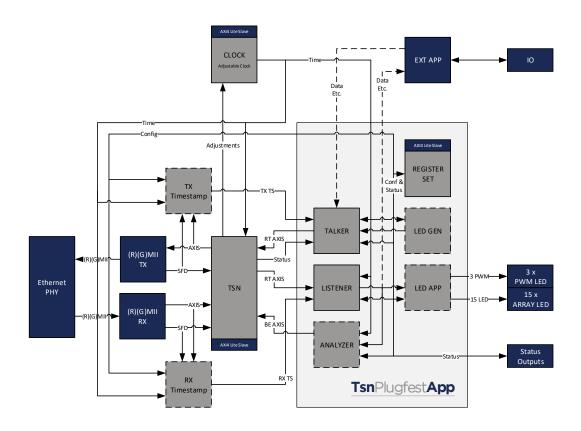

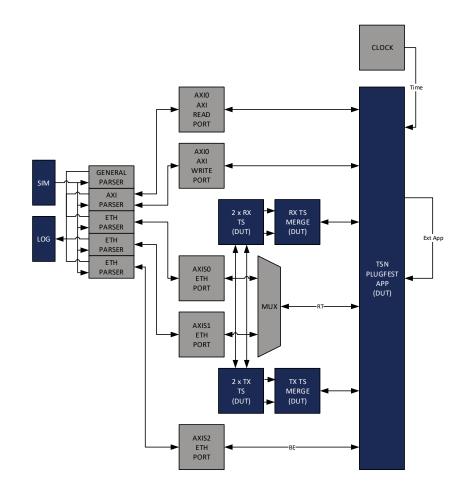

## 1.3 Architecture

The core is split up into different functional blocks for reduction of the complexity, modularity and maximum reuse of blocks. The interfaces between the functional blocks are kept as small as possible for easier understanding of the core.

Figure 2: Architecture Block Diagram

The Block diagram shows only one PHY, for multiple PHYs there are also Timestamp Mergers which allow to get the timestamps from multiple instances.

#### **Register Set**

This block allows reading status values and writing configuration.

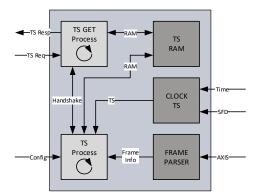

#### **RX and TX Timestampers**

These blocks take timestamps of the OPC/UA Real-time frames as close as possible to the PHY. They get the Data and the Start of Frame Delimiter (SFD) of the (R)(G)MII Interface Adapters which are part of the TSN core (but separated to get access to these signals). The block stores a timestamp based on the Talker Identifier and the Frame Sequence Number. The Talker and Listener can then request the timestamp for this specific frame.

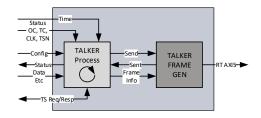

#### Talker

This block sends periodic OPC/UA Real-time frames with definable interval, offset, delay etc. The payload, which can come from Registers, a LED Pattern Generator or a Custom External Application is encapsulated into the frame without the need of knowledge of the frame.

It also takes a timestamp when the frame was actually sent onto the cable and will put the sending timestamp into the next frame.

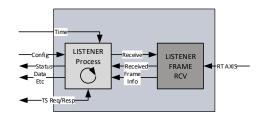

#### Listener

This block receives the OPC/UA Real-time frames, parses it and extracts meta data as well as associating a receive timestamp when the frame was actually received on the cable. The data and meta information is then provided to the LED PWM Application and to the Custom External Application which can decide to use the Data or not and also to the Analyzer for further analysis.

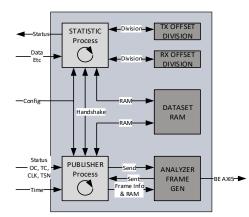

#### Analyzer

This block receives the data and meta information from the listener, analyzes it and creates statistics. The statics result is then periodically sent via a UDP/IP OPC/UA Best-effort frames so a centralized node can collect also statistics from all other nodes to get a picture of the Network.

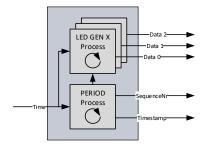

#### **LED Generator**

This block is an LED Pattern Generator which generates a brightness pattern for 3 LED as a percentage between 0 and 100. It will create a pattern with slowly overlapping and fading LEDs.

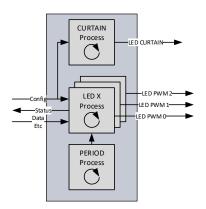

#### **LED PWM Application**

This block converts the received LED brightness into a PWM signal which is fed to 3 LEDs. In addition, it also provides a 15bit Binary array representing the light curtain value.

# 2 TSN Plugfest App Basics

The IIC TSN Plugfest Application is built of several components which shall allow tests and measurements as well as data transfer as demo for the demo wall. It can be also used to transfer custom data.

The specifications are available under the IIC terms. If you are not a Member of the IIC you can get one for free to access the documents by signing some NDAs.

The "IIC Interoperability Application v0.3" specification can be found here: <u>https://engage.iiconsortium.org/wg/TBTSN/document/11502</u> The "LED Strip Demo Application v0.3" specification can be found here: <u>https://engage.iiconsortium.org/wg/TBTSN/document/11373</u>

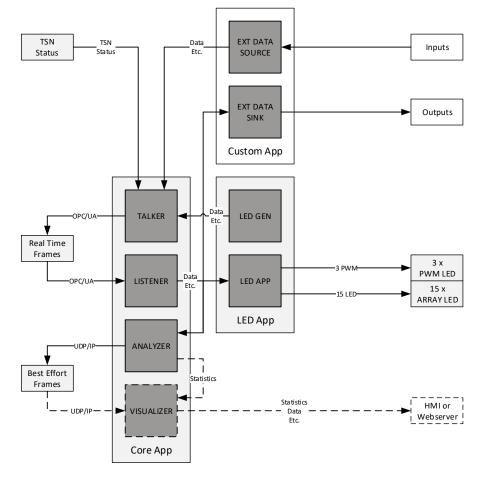

## 2.1 Concept

The application is made of several sub-components (not all shown and not all implemented)

Figure 3: Concept

## 2.1.1 Core Application

The Core part of the IIC TSN Plugfest Application is formed from the following subcomponents:

- Talker

- Listener

- Analyzer (Analysis and Result Publication)

- Visualizer

## 2.1.1.1 Talker

Transmit periodically OPC/UA frames at a specific offset (also as information in the frame) as Layer2 Multicast frames. The frames contain information about the TSN and Talker (802.1AS, Hardware Timestamping, Data Valid) status, a Talker ID, the vendor and device names, as well as sequence numbers and timestamps of the application, of each sent frame and a precise timestamp when the last frame was sent. In addition, it contains 32byte of data and an 8bit application identifier to determine what kind of data it is. The data can be provided either from registers, a LED Generator or any custom Application which wants to have the data encapsulated in this OPC/UA frame.

The idea is that every node sends these frames, and every node receives the frames from all other nodes, so it can do statistics.

## 2.1.1.2 Listener

Receives the frames from all other Talkers and associates the frame with a precise timestamp when the frame was received.

It parses the frame and extracts all meta data which it then provides to the other sub-components together with the receive timestamp.

## 2.1.1.3 Analyzer

This module makes statistics over the received Talker frames. It calculates the delay through the network, the send and receive offsets in the interval and for each value the min, max and current value. In addition, it checks if frames were missed or if an application updated was missed. All this is done on a per Talker base. The results of these statistic are then sent periodically (1/s) via an UDP/IP Multicast frame (also OPC/UA UADP) to all other nodes, so each node gets the statistics of each other node. Since the maximum size of an Ethernet frame is limited to 1500bytes only 23 nodes can be sent with one frame. (this might change in the future). It shall also provide the local statistics to the Visualizer, if implemented.

#### 2.1.1.4 Visualizer

This module shall receive the statistics of all other nodes and shall visualize them in some way (HMI, Webserver, ...). This is not defined yet.

## 2.1.2 LED Application

The IIC defined a specific Application which was implemented by most vendors to run a demo. The Demo consists of 3 LEDs which are adjusted in their brightness via a PWM generator and a 15 LED array which shows the state of the light curtain. The source for the brightness and light curtain is a Sick device.

The Application Identifier for the LED Application is 0x01.

The first 3 bytes of the data payload represent the brightness of the 3 LEDs as a percentage (0-100). The next two bytes form a 16bit value which represent the light curtain of the Sick device. Only the lower 15bits are used since the Sick device has only 15 light beams.

The other Data bytes are don't cares.

The LED part is formed out of the following two sub-components:

- LED Gen

- LED App

#### 2.1.2.1 LED Gen

This is a LED pattern generator which feeds the Talker with the Application Identifier, the actual Data, an Application Timestamp and an Application Sequence Number. What kind of pattern shall be generated and also the refresh rate is up to the implementer (our implementation is described later).

#### 2.1.2.2 LED App

This is a PWM generator for the brightness of the LEDs. It receives the frame information from the Listener and checks if the Application Identifier is correct and optionally also if the Talker Identification matches a configured value. Whenever a new frame is received which matches the criteria it will calculate a pulse width value for the PWM per LED. The PWM period and also the refresh rate is up to the implementer.

## 2.1.3 Custom Application

A Custom Application is basically the same as the LED Application. It shall have a data sink connected to the Listener and a data source connected to the Talker.

There are many unused Application identifiers which can be used to send custom data with the same frame format.

## **3** Register Set

This is the register set of the TSN Plugfest App. It is accessible via AXI4Lite Memory Mapped. All registers are 32bit wide, no burst access, no unaligned access, no byte enables, no timeouts are supported. Register address space is not contiguous. Register addresses are only offsets in the memory area where the core is mapped in the AXI interconnects. Non existing register access in the mapped memory area is answered with a slave decoding error.

## 3.1 Register Overview

| <b>–</b> • • • | <u> </u>  |

|----------------|-----------|

| Registerset    | ()verview |

| 1.0913101301   |           |

| Name                                | Description                                                   | Offset     | Access |  |

|-------------------------------------|---------------------------------------------------------------|------------|--------|--|

| Tsn PlugfestAppControl Reg          | Tsn PlugfestApp Control Register                              | 0x00000000 | RW     |  |

| Tsn PlugfestAppStatus Reg           | Tsn PlugfestApp Error Status Register                         | 0x00000004 | WC     |  |

| Tsn PlugfestAppVersion Reg          | Tsn PlugfestApp Version Register                              | 0x000000C  | RO     |  |

| Tsn PlugfestAppTalkerControl Reg    | Tsn PlugfestApp Talker Control Register                       | 0x00000100 | RW     |  |

| Tsn PlugfestAppTalkerMac1 Reg       | Tsn PlugfestApp Talker Mac 1 Register                         | 0x00000104 | RW     |  |

| Tsn PlugfestAppTalkerMac2 Reg       | Tsn PlugfestApp Talker Mac 2 Register                         | 0x00000108 | RW     |  |

| Tsn PlugfestAppTalkerId Reg         | Tsn PlugfestApp Talker Id Register                            | 0x0000010C | RW     |  |

| Tsn PlugfestAppTalkerDelay Reg      | Tsn PlugfestApp Talker Delay Register                         | 0x00000110 | RW     |  |

| Tsn PlugfestAppTalkerOffset Reg     | Tsn PlugfestApp Talker Offset Register                        | 0x00000114 | RW     |  |

| Tsn PlugfestAppTalkerInterval Reg   | Tsn PlugfestApp Talker Interval Register                      | 0x00000118 | RW     |  |

| Tsn PlugfestAppTalkerVlan Reg       | Tsn PlugfestApp Talker Configuration VLAN Register            | 0x0000011C | RW     |  |

| Tsn PlugfestAppTalkerAppId Reg      | Tsn PlugfestApp Talker Application Identifier Register        | 0x0000014C | RW     |  |

| Tsn PlugfestAppTalkerAppDataOto3 Re | Tsn PlugfestApp Talker Application Data Bytes 0 to 3 Register | 0x00000150 | RW     |  |

| Tsn PlugfestAppTalkerAppData4to7 Re | Tsn PlugfestApp Talker Application Data Bytes 4 to 7 Register | 0x00000154 | RW     |  |

|                                       |                                                                 | -          |    |

|---------------------------------------|-----------------------------------------------------------------|------------|----|

| Tsn PlugfestAppTalkerAppData8to11 Reg | Tsn PlugfestApp Talker Application Data Bytes 8 to 11 Register  | 0x00000158 | RW |

| Tsn PlugfestAppTalkerAppData12to15    | Tsn PlugfestApp Talker Application Data Bytes 12 to 15 Register | 0x0000015C | RW |

| Reg                                   |                                                                 |            |    |

| Tsn PlugfestAppTalkerAppData16to19    | Tsn PlugfestApp Talker Application Data Bytes 16 to 19 Register | 0x00000160 | RW |

| Reg                                   |                                                                 |            |    |

| Tsn PlugfestAppTalkerAppData20to23    | Tsn PlugfestApp Talker Application Data Bytes 20 to 23 Register | 0x00000164 | RW |

| Reg                                   |                                                                 |            |    |

| Tsn PlugfestAppTalkerAppData24to27    | Tsn PlugfestApp Talker Application Data Bytes 24 to 27 Register | 0x00000168 | RW |

| Reg                                   |                                                                 |            |    |

| Tsn PlugfestAppTalkerAppData28to31    | Tsn PlugfestApp Talker Application Data Bytes 28 to 31 Register | 0x0000016C | RW |

| Reg                                   |                                                                 |            |    |

| Tsn PlugfestAppListenerControl Reg    | Tsn PlugfestApp Listener Control Register                       | 0x0000200  | RW |

| Tsn PlugfestAppListenerDelay Reg      | Tsn PlugfestApp Listener Configuration Delay Register           | 0x00000210 | RW |

| Tsn PlugfestAppListenerVlan Reg       | Tsn PlugfestApp Listener Configuration VLAN Register            | 0x0000021C | RW |

| Tsn PlugfestAppAnalyzerControl Reg    | Tsn PlugfestApp Analyzer Control Register                       | 0x0000300  | RW |

| Tsn PlugfestAppAnalyzerIp Reg         | Tsn PlugfestApp Analyzer Configuration Source Ip Register       | 0x0000304  | RW |

| Tsn PlugfestAppAnalyzerUdpPort Reg    | Tsn PlugfestApp Analyzer Configuration UDP Source Port Regis-   | 0x00000308 | RW |

|                                       | ter                                                             |            |    |

| Tsn PlugfestAppAnalyzerVlan Reg       | Tsn PlugfestApp Analyzer Configuration VLAN Register            | 0x0000031C | RW |

| Tsn PlugfestAppAppLedControl Reg      | Tsn PlugfestApp AppLed Control Register                         | 0x00001000 | RW |

| Tsn PlugfestAppAppLedId Reg           | Tsn PlugfestApp AppLed Configuration Talker Identifier Register | 0x0000100C | RW |

| Tsn PlugfestAppAppLedVlan Reg         | Tsn PlugfestApp AppLed Configuration VLAN Register              | 0x0000101C | RW |

| Tsn PlugfestAppAppLedVlan Reg         | Tsn PlugfestApp AppLed Configuration VLAN Register              | 0x0000101C | RW |

Table 4:Register Set Overview

## 3.2 Register Descriptions

#### 3.2.1 General

#### 3.2.1.1 TSN Plugfest App Control Register

Used for general control over the TSN Plugfest App core, all configurations on the core shall only be done when disabled. The Enable acts as general enable and disable for all other components, meaning that only when this is enabled the other enabled sub-cores will be enabled as well, the same applies for disabling, it disables al other sub-cores. The APP\_EXT bit signals if the external Application interface shall be used as Data source.

| Tsn PlugfestAppControl Reg<br>Reg Description                                   |                                  |                 |

|---------------------------------------------------------------------------------|----------------------------------|-----------------|

|                                                                                 |                                  |                 |

| 31     30     29     28     27     26     25     24     23     22     21     20 | 9 18 17 16 15 14 13 12 11 10 9 8 | 7 6 5 4 3 2 1 0 |

|                                                                                 |                                  |                 |

|                                                                                 |                                  |                 |

|                                                                                 |                                  |                 |

|                                                                                 | E X 1                            |                 |

| 1                                                                               |                                  | B<br>▼          |

|                                                                                 |                                  | Ż               |

|                                                                                 |                                  |                 |

|                                                                                 |                                  |                 |

|                                                                                 |                                  |                 |

| RO                                                                              | R R                              | R               |

|                                                                                 | W                                | W               |

|                                                                                 | Reset: 0x0000000                 |                 |

|                                                                                 | Offset: 0x0000                   |                 |

| Name    | Description                                      | Bits       | Access |

|---------|--------------------------------------------------|------------|--------|

| -       | Reserved, read 0                                 | Bit: 31:17 | RO     |

| APP_EXT | Use External Application interface (else LedGen) | Bit: 16    | RW     |

| -       | Reserved, read 0                                 | Bit: 15:1  | RO     |

| ENABLE  | Enable                                           | Bit: O     | RW     |

#### 3.2.1.2 Tsn Plugfest App Error Status Register

Shows the current status of the TSN Plugfest App. Each sub-core has its own error bit, all error bits are sticky and must be cleared by writing a 1 to the corresponding bit

| Tsn PlugfestAppStatus Reg           |              |                |                |              |      |    |    |    |    |    |   |    |   |   |   |   |   |   |   |       |

|-------------------------------------|--------------|----------------|----------------|--------------|------|----|----|----|----|----|---|----|---|---|---|---|---|---|---|-------|

| Reg Description                     |              |                |                |              |      |    |    |    |    |    |   |    |   |   |   |   |   |   |   |       |

| 31 30 29 28 27 26 25 24 23 22 21 20 | 19           | 18             | 17             | 16           | 15   | 14 | 13 | 12 | 11 | 10 | 9 | 8  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

| T                                   | APPLED_ERROR | ANALYZER_ERROR | LISTENER_ERROR | TALKER_ERROR |      |    |    |    |    |    |   | T  |   |   |   |   |   |   |   | ERROR |

| RO                                  | WC           | WC             | WC             | WC           |      |    |    |    |    |    |   | RO |   |   |   |   |   |   |   | WC    |

| Reset: 0x0000000                    |              |                |                |              |      |    |    |    |    |    |   |    |   |   |   |   |   |   |   |       |

|                                     |              |                | Offs           | set: 0>      | <00( | )4 |    |    |    |    |   |    |   |   |   |   |   |   |   |       |

| Name           | Description                    | Bits       | Access |

|----------------|--------------------------------|------------|--------|

| -              | Reserved, read O               | Bit: 31:20 | RO     |

| APPLED_ERROR   | Application LED Error (sticky) | Bit: 19    | WC     |

| ANALYZER_ERROR | Analyzer Error (sticky)        | Bit: 18    | WC     |

| LISTENER_ERROR | Listener Error (sticky)        | Bit: 17    | WC     |

| TALKER_ERROR   | Talker Error (sticky)          | Bit: 16    | WC     |

| -              | Reserved, read O               | Bit: 15:1  | RO     |

| ERROR Error (sti |  | Bit: O | WC |

|------------------|--|--------|----|

|------------------|--|--------|----|

## 3.2.1.3 TSN Plugfest App Version Register

BLABAL

| 200 | Decerti | +:    |    |    |    |    |    |    |    |    |    |    |       |       |         |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|-----|---------|-------|----|----|----|----|----|----|----|----|----|----|-------|-------|---------|-----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| keg | Descrip | otion |    |    |    |    |    |    |    |    |    |    |       |       |         |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| 31  | 30 29   | 28    | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17    | 16    | 15      | 14  | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | ( |

|     |         |       |    |    |    |    |    |    |    |    |    |    |       |       |         |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |         |       |    |    |    |    |    |    |    |    |    |    |       |       |         |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |         |       |    |    |    |    |    |    |    |    |    |    |       |       |         |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |         |       |    |    |    |    |    |    |    |    |    |    |       |       |         |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |         |       |    |    |    |    |    |    |    |    |    |    |       |       | Z       |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |         |       |    |    |    |    |    |    |    |    |    |    |       |       |         |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |         |       |    |    |    |    |    |    |    |    |    |    |       |       | /ERSION |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |         |       |    |    |    |    |    |    |    |    |    |    |       |       | Щ       |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |         |       |    |    |    |    |    |    |    |    |    |    |       |       |         |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |         |       |    |    |    |    |    |    |    |    |    |    |       |       |         |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |         |       |    |    |    |    |    |    |    |    |    |    |       |       |         |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |         |       |    |    |    |    |    |    |    |    |    |    |       |       |         |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |         |       |    |    |    |    |    |    |    |    |    |    |       | R     | 0       |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |         |       |    |    |    |    |    |    |    |    |    | F  | Reset | : OxX | XXX     | XXX | Х  |    |    |    |   |   |   |   |   |   |   |   |   | _ |

|     |         |       |    |    |    |    |    |    |    |    |    |    |       |       |         |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Name    | Description            | Bits      | Access |

|---------|------------------------|-----------|--------|

| VERSION | Version of the IP core | Bit: 31:0 | RO     |

## 3.2.2 Talker

#### 3.2.2.1 TSN Plugfest App Talker Control Register

Used for general control over the Talker, all configurations on the core shall only be done when disabled.

| Tsn PlugfestAppTalkerControl Reg                                                              |           |         |     |             |    |    |    |    |    |   |    |   |   |   |   |   |   |   |            |        |

|-----------------------------------------------------------------------------------------------|-----------|---------|-----|-------------|----|----|----|----|----|---|----|---|---|---|---|---|---|---|------------|--------|

| Reg Description                                                                               |           |         |     |             |    |    |    |    |    |   |    |   |   |   |   |   |   |   |            |        |

| 31     30     29     28     27     26     25     24     23     22     21     20     19     18 | 17        | 16      | 5 1 | 15          | 14 | 13 | 12 | 11 | 10 | 9 | 8  | 3 | 7 | 6 | 5 | 4 | 3 | 2 | 1          | 0      |

| 1                                                                                             | VLAN      | 000 RFG | צן  |             |    |    |    |    |    |   | ı  |   |   |   |   |   |   |   | RESET_STAT | ENABLE |

| RO                                                                                            | RW        | RW      |     |             |    |    |    |    |    |   | RO |   |   |   |   |   |   |   | RW         | RW     |

|                                                                                               | Rese<br>O |         |     | 000<br>×010 |    | )  |    |    |    |   |    |   |   |   |   |   |   |   |            |        |

| Name      | Description                                                  | Bits       | Access |

|-----------|--------------------------------------------------------------|------------|--------|

| -         | Reserved, read 0                                             | Bit: 31:18 | RO     |

| VLAN      | Send VLAN as specified in Reg (else 0xABB8)                  | Bit: 17    | RW     |

| APP_REG   | Use Register values as Application data (else LedGen or Ext) | Bit: 16    | RW     |

| -         | Reserved, read 0                                             | Bit: 15:2  | RO     |

| REST_STAT | Set the Reset Statistics bit (must be cleared again)         | Bit: 1     | RW     |

| ENABLE | Enable | Bit: O | RW |

|--------|--------|--------|----|

|--------|--------|--------|----|

## 3.2.2.2TSN Plugfest App Talker MAC 1 Register

Source MAC of the Talker frames.

| Reg Description         |                         |                        |                 |

|-------------------------|-------------------------|------------------------|-----------------|

|                         |                         | 15 14 17 10 11 10 0 0  |                 |

| 31 30 29 28 27 26 25 24 | 23 22 21 20 19 18 17 16 | 15 14 13 12 11 10 9 8  | 7 6 5 4 3 2 1 0 |

|                         |                         |                        |                 |

|                         |                         |                        |                 |

|                         |                         |                        |                 |

|                         |                         |                        |                 |

| C(3)                    | (2)                     | C(1)                   | 0               |

| Ō                       | Ų                       | O T                    | Q               |

| Ψ                       | Σ                       | Υ<br>Σ                 | $\searrow$      |

| —                       | —                       |                        | 2               |

|                         |                         |                        |                 |

|                         |                         |                        |                 |

|                         |                         |                        |                 |

| RW                      | RW                      | RW                     | RW              |

|                         | Reset: 0x00             | 000000                 |                 |

|                         | Offset: 0               | $) \sim \cap 1 \cap A$ |                 |

| Name   | Description       | Bits      | Access |

|--------|-------------------|-----------|--------|

| MAC(3) | Source MAC Byte 3 | Bit:31:24 | RW     |

| MAC(2) | Source MAC Byte 2 | Bit:23:16 | RW     |

| MAC(1) | Source MAC Byte 1 | Bit:15:8  | RW     |

| MAC(0) | Source MAC Byte 0 | Bit:7:0   | RW     |

## 3.2.2.3TSN Plugfest App Talker MAC 2Register

Source MAC of the Talker frames.

| Tsn PlugfestAppTalkerMac2 Reg                                                                        |                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reg Description                                                                                      |                                                                                                                                                                         |

| 31     30     29     28     27     26     25     24     23     22     21     20     19     18     17 | 5         15         14         13         12         11         10         9         8         7         6         5         4         3         2         1         0 |

| r                                                                                                    | MAC(5)<br>MAC(4)                                                                                                                                                        |

| RO                                                                                                   | RW RW                                                                                                                                                                   |

|                                                                                                      | x0000000                                                                                                                                                                |

| (                                                                                                    | t: 0x0108                                                                                                                                                               |

| Name   | Description       | Bits      | Access |

|--------|-------------------|-----------|--------|

| -      | Reserved, read 0  | Bit:31:16 | RO     |

| MAC(5) | Source MAC Byte 5 | Bit:15:8  | RW     |

| MAC(4) | Source MAC Byte 4 | Bit:7:0   | RW     |

## 3.2.2.4 TSN Plugfest App Talker Id Register

Talker Id of the Talker frames. Based on this, the Destination MAC (lower 2 bytes) is calculated.

| Tsn PlugfestAppTalkerId Reg                                                                                                 |                  |                                 |     |

|-----------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------|-----|

| Reg Description                                                                                                             |                  |                                 |     |

| 31         30         29         28         27         26         25         24         23         22         21         20 | 9 18 17 16 15 14 | 14 13 12 11 10 9 8 7 6 5 4 3 2  | 1 0 |

|                                                                                                                             |                  |                                 |     |

|                                                                                                                             |                  |                                 |     |

|                                                                                                                             |                  |                                 |     |

|                                                                                                                             |                  | $\underline{\Box}_{\mathbf{I}}$ |     |

|                                                                                                                             |                  |                                 |     |

| 1                                                                                                                           |                  | Д                               |     |

|                                                                                                                             |                  | AL                              |     |

|                                                                                                                             |                  | ⊢ ⊢                             |     |

|                                                                                                                             |                  |                                 |     |

|                                                                                                                             |                  |                                 |     |

| RO                                                                                                                          |                  | RW                              |     |

| KU                                                                                                                          | Reset: 0x000000  |                                 |     |

|                                                                                                                             | Offset: 0x010C   |                                 |     |

|                                                                                                                             | Unset. 0x010C    |                                 |     |

| Name      | Description                | Bits      | Access |

|-----------|----------------------------|-----------|--------|

| -         | Reserved, read 0           | Bit:31:16 | RO     |

| TALKER_ID | Talker ID (use only 0-255) | Bit:15:0  | RW     |

#### 3.2.2.5TSN Plugfest App Talker Delay Register

Delay between the core and the actual frame being sent by the PHY. This delay is taken into account to start sending of the frame early enough so it reaches the output port at the right time.

| Tsi | ו Plugi         | estA | νрр٦ | alke | erDe | lay | Reg | J  |    |    |    |    |       |       |                 |      |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|-----|-----------------|------|------|------|------|-----|-----|----|----|----|----|----|-------|-------|-----------------|------|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| Reg | Reg Description |      |      |      |      |     |     |    |    |    |    |    |       |       |                 |      |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| 31  | 30 29           | 28   | 27   | 26   | 25   | 24  | 23  | 22 | 21 | 20 | 19 | 18 | 17    | 16    | 15              | 14   | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|     |                 |      |      |      |      |     |     |    |    |    |    |    |       |       |                 |      |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |                 |      |      |      |      |     |     |    |    |    |    |    |       |       |                 |      |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |                 |      |      |      |      |     |     |    |    |    |    |    |       |       |                 |      |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |                 |      |      |      |      |     |     |    |    |    |    |    |       |       | ≻               |      |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |                 |      |      |      |      |     |     |    |    |    |    |    |       | -     | $\triangleleft$ |      |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |                 |      |      |      |      |     |     |    |    |    |    |    |       | l     | ΓL              |      |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |                 |      |      |      |      |     |     |    |    |    |    |    |       |       |                 |      |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |                 |      |      |      |      |     |     |    |    |    |    |    |       |       |                 |      |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |                 |      |      |      |      |     |     |    |    |    |    |    |       |       |                 |      |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |                 |      |      |      |      |     |     |    |    |    |    |    |       | R     | W               |      |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |                 |      |      |      |      |     |     |    |    |    |    | F  | Reset | : OxC |                 | 0000 | С  |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |                 |      |      |      |      |     |     |    |    |    |    |    |       | fset: |                 |      |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |                 |      |      |      |      |     |     |    |    |    |    |    |       |       |                 |      |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Name  | Description                                                                                                                                                                             | Bits      | Access |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------|

| DELAY | TX Delay in Nanoseconds, used to send the frame early<br>enough that it will be sent at the right moment (at OFF-<br>SET), also needed for internal timestamp compensation<br>when used | Bit: 31:0 | RW     |

## 3.2.2.6TSN Plugfest App Talker Offset Register

Desired offset within a second when the frame sending shall start.

| Tsr | Plugfe  | estA  | рр٦ | Talke | erOf | fset | Re | g  |    |    |    |    |    |             |      |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|-----|---------|-------|-----|-------|------|------|----|----|----|----|----|----|----|-------------|------|-----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| Reg | Descrip | otion |     |       |      |      |    |    |    |    |    |    |    |             |      |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| 31  | 30 29   | 28    | 27  | 26    | 25   | 24   | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16          | 15   | 14  | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|     |         |       |     |       |      |      |    |    |    |    |    |    |    |             |      |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |         |       |     |       |      |      |    |    |    |    |    |    |    |             |      |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |         |       |     |       |      |      |    |    |    |    |    |    |    |             |      |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |         |       |     |       |      |      |    |    |    |    |    |    |    | F           |      |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |         |       |     |       |      |      |    |    |    |    |    |    |    | Ц<br>V      | )    |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |         |       |     |       |      |      |    |    |    |    |    |    |    | Ц<br>Ц<br>С | -    |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |         |       |     |       |      |      |    |    |    |    |    |    |    | C           | )    |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |         |       |     |       |      |      |    |    |    |    |    |    |    |             |      |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |         |       |     |       |      |      |    |    |    |    |    |    |    |             |      |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |         |       |     |       |      |      |    |    |    |    |    |    |    |             |      |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |         |       |     |       |      |      |    |    |    |    |    |    |    | RW          |      |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |         |       |     |       |      |      |    |    |    |    |    | F  |    | : 0x0(      |      |     | С  |    |    |    |   |   |   |   |   |   |   |   |   |   |

|     |         |       |     |       |      |      |    |    |    |    |    |    | Ot | fset: (     | )x01 | 114 |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Name   | Description                                       | Bits      | Access |

|--------|---------------------------------------------------|-----------|--------|

| OFFSET | TX Offset from beginning of Second in Nanoseconds | Bit: 31:0 | RW     |

## 3.2.2.7TSN Plugfest App Talker Interval Register

Sending interval of the Talker frames..

|                 | Isn PlugfestAppTalkerInterval Reg |    |    |    |    |    |    |    |    |    |    |    |    |        |        |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|-----------------|-----------------------------------|----|----|----|----|----|----|----|----|----|----|----|----|--------|--------|-----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| Reg Description |                                   |    |    |    |    |    |    |    |    |    |    |    |    |        |        |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| 31              | 30 29                             | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16     | 15     | 14  | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|                 |                                   |    |    |    |    |    |    |    |    |    |    |    |    |        |        |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|                 |                                   |    |    |    |    |    |    |    |    |    |    |    |    |        |        |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|                 |                                   |    |    |    |    |    |    |    |    |    |    |    |    |        |        |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| $\succ$         |                                   |    |    |    |    |    |    |    |    |    |    |    |    |        |        |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|                 | $\forall$                         |    |    |    |    |    |    |    |    |    |    |    |    |        |        |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|                 |                                   |    |    |    |    |    |    |    |    |    |    |    |    | ĺ      | Ц<br>Ц |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|                 |                                   |    |    |    |    |    |    |    |    |    |    |    |    | ł      | Z      |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|                 |                                   |    |    |    |    |    |    |    |    |    |    |    |    | 1      |        |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|                 |                                   |    |    |    |    |    |    |    |    |    |    |    |    |        |        |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|                 |                                   |    |    |    |    |    |    |    |    |    |    |    |    |        |        |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|                 |                                   |    |    |    |    |    |    |    |    |    |    |    |    |        |        |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|                 |                                   |    |    |    |    |    |    |    |    |    |    |    |    | R'     |        | 000 |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|                 |                                   |    |    |    |    |    |    |    |    |    |    | F  |    | : OxC  |        |     | U  |    |    |    |   |   |   |   |   |   |   |   |   |   |

|                 |                                   |    |    |    |    |    |    |    |    |    |    |    | Of | ffset: | 0x0    | 118 |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Name     | Description                | Bits      | Access |

|----------|----------------------------|-----------|--------|

| INTERVAL | TX Interval in Nanoseconds | Bit: 31:0 | RW     |

#### 3.2.2.8TSN Plugfest App Talker VLAN Register

If VLAN is not enabled it will take the default VLAN tag defined in the specification (0xABB8), othwise it takes the VLAN from this register.

| Tsn | Plu | ıgfe  | stA  | pp7 | Falke | erVl | an F | Reg |    |    |    |    |    |       |       |      |      |                |    |    |    |   |   |               |   |   |   |   |   |   |   |

|-----|-----|-------|------|-----|-------|------|------|-----|----|----|----|----|----|-------|-------|------|------|----------------|----|----|----|---|---|---------------|---|---|---|---|---|---|---|

| Reg | Des | cript | tion |     |       |      |      |     |    |    |    |    |    |       |       |      |      |                |    |    |    |   |   |               |   |   |   |   |   |   |   |

| 31  | 30  | 29    | 28   | 27  | 26    | 25   | 24   | 23  | 22 | 21 | 20 | 19 | 18 | 17    | 16    | 15   | 14   | 13             | 12 | 11 | 10 | 9 | 8 | 7             | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|     |     |       |      |     |       |      |      |     |    |    |    |    |    |       |       |      |      |                |    |    |    |   |   |               |   |   |   |   |   |   |   |

|     |     |       |      |     |       |      |      |     |    |    |    |    |    |       |       |      |      |                |    |    |    |   |   |               |   |   |   |   |   |   |   |

|     |     |       |      |     |       |      |      |     |    |    |    |    |    |       |       |      |      |                |    |    |    |   |   |               |   |   |   |   |   |   |   |

|     |     |       |      |     |       |      |      |     |    |    |    |    |    |       |       |      |      |                |    |    |    |   |   |               |   |   |   |   |   |   |   |

|     |     |       |      |     |       |      |      |     |    |    |    |    |    |       |       |      |      |                |    |    |    |   |   |               |   |   |   |   |   |   |   |

|     |     |       |      |     |       |      |      | I   |    |    |    |    |    |       |       |      |      |                |    |    |    |   |   | <<br>√<br>L > |   |   |   |   |   |   |   |

|     |     |       |      |     |       |      |      |     |    |    |    |    |    |       |       |      |      |                |    |    |    |   |   | >             |   |   |   |   |   |   |   |

|     |     |       |      |     |       |      |      |     |    |    |    |    |    |       |       |      |      |                |    |    |    |   |   |               |   |   |   |   |   |   |   |

|     |     |       |      |     |       |      |      |     |    |    |    |    |    |       |       |      |      |                |    |    |    |   |   |               |   |   |   |   |   |   |   |

|     |     |       |      |     |       |      |      |     |    |    |    |    |    |       |       |      |      |                |    |    |    |   |   |               |   |   |   |   |   |   |   |

|     |     |       |      |     |       |      | P    | 20  |    |    |    |    |    |       |       |      |      |                |    |    |    |   | 5 | RW            |   |   |   |   |   |   |   |

|     |     |       |      |     |       |      |      | .0  |    |    |    |    | F  | ?eset | : OxC | 000  | 0000 | $\overline{)}$ |    |    |    |   | Г | ~ ~ ~         |   |   |   |   |   |   |   |

|     |     |       |      |     |       |      |      |     |    |    |    |    | 1  |       | fset: |      |      | 0              |    |    |    |   |   |               |   |   |   |   |   |   |   |

|     |     |       |      |     |       |      |      |     |    |    |    |    |    | U     | iset. | 0.00 |      |                |    |    |    |   |   |               |   |   |   |   |   |   |   |

| Name | Description                 | Bits      | Access |

|------|-----------------------------|-----------|--------|

| -    | Reserved, read O            | Bit:31:16 | RO     |

| VLAN | VLAN Tag to send if enabled | Bit:15:0  | RW     |

## 3.2.2.9TSN Plugfest App Talker App IdRegister

Application ID of the Talker frames, only used when the Register mode is used

| Tsn PlugfestAppTalkerAppId Reg |                              |                              |  |  |  |  |  |  |  |  |  |  |  |

|--------------------------------|------------------------------|------------------------------|--|--|--|--|--|--|--|--|--|--|--|

| Reg Description                |                              |                              |  |  |  |  |  |  |  |  |  |  |  |

| 31 30 29 28 27 26 25 24 23 22  | 2 21 20 19 18 17 16 15 14 13 | 12 11 10 9 8 7 6 5 4 3 2 1 0 |  |  |  |  |  |  |  |  |  |  |  |

|                                |                              |                              |  |  |  |  |  |  |  |  |  |  |  |

|                                |                              |                              |  |  |  |  |  |  |  |  |  |  |  |

|                                |                              |                              |  |  |  |  |  |  |  |  |  |  |  |

|                                |                              |                              |  |  |  |  |  |  |  |  |  |  |  |

|                                | 1                            |                              |  |  |  |  |  |  |  |  |  |  |  |

|                                |                              |                              |  |  |  |  |  |  |  |  |  |  |  |

|                                |                              |                              |  |  |  |  |  |  |  |  |  |  |  |

|                                |                              |                              |  |  |  |  |  |  |  |  |  |  |  |

|                                |                              |                              |  |  |  |  |  |  |  |  |  |  |  |

|                                | RO                           | RW                           |  |  |  |  |  |  |  |  |  |  |  |

| Reset: 0x0000000               |                              |                              |  |  |  |  |  |  |  |  |  |  |  |

|                                | Offset: 0x014C               |                              |  |  |  |  |  |  |  |  |  |  |  |

| Name   | Description                                                                                               | Bits     | Access |

|--------|-----------------------------------------------------------------------------------------------------------|----------|--------|

| -      | Reserved, read 0                                                                                          | Bit:31:8 | RO     |

| APP_ID | Application Identifier (0: undefined, 1: LedStrip, 2: Motion control, 3: Motion listener, 4-255 reserved) | Bit:7:0  | RW     |

## 3.2.2.10 TSN Plugfest App Talker Data Registers

Data Bytes of the Talker frames. The Talker will always send 32 Bytes of Data.

| Tsn PlugfestAppTalkerData[ | x] Reg                  |                       |                   |

|----------------------------|-------------------------|-----------------------|-------------------|

| Reg Description            |                         |                       |                   |

| 31 30 29 28 27 26 25 24    | 23 22 21 20 19 18 17 16 | 15 14 13 12 11 10 9 8 | 7 6 5 4 3 2 1 0   |

|                            |                         |                       |                   |

|                            |                         |                       |                   |

|                            | $\sim$                  |                       | 2                 |

| Ź                          | + 7                     | +                     | +<br>Z            |

| TAC                        | A(N+1)                  | A(N+2)                | $\langle \rangle$ |

| -AC                        | E E                     | AT,                   | AT,               |

|                            | DA                      | Õ                     | Ô                 |

|                            |                         |                       |                   |

|                            |                         |                       |                   |

| RW                         | RW                      | RW                    | RW                |

|                            | Reset: 0x0              | 000000                |                   |

|                            | Offset: 0x0             | 150 - 0x16C           |                   |

| Name      | Description   | Bits      | Access |

|-----------|---------------|-----------|--------|

| DATA(N)   | Data Byte N   | Bit:31:24 | RW     |

| DATA(N+1) | Data Byte N+1 | Bit:23:16 | RW     |

| DATA(N+2) | Data Byte N+2 | Bit:15:8  | RW     |

| DATA(N+3) | Data Byte N+3 | Bit:7:0   | RW     |

#### 3.2.3 Listener

#### 3.2.3.1 TSN Plugfest App Listener Control Register

Used for general control over the Listener, all configurations on the core shall only be done when disabled.

| Tsn PlugfestAppListenerControl Reg                                                                                                     |             |      |       |    |    |    |    |    |   |   |   |   |   |   |   |   |   |        |

|----------------------------------------------------------------------------------------------------------------------------------------|-------------|------|-------|----|----|----|----|----|---|---|---|---|---|---|---|---|---|--------|

| Reg Description                                                                                                                        |             |      |       |    |    |    |    |    |   |   |   |   |   |   |   |   |   |        |

| 31         30         29         28         27         26         25         24         23         22         21         20         19 | 18          | 17   | 16 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0      |

| ı                                                                                                                                      | IGNORE_VLAN | VLAN |       |    |    |    |    |    |   | I |   |   |   |   |   |   |   | ENABLE |

| RO RW RW RO RO RW                                                                                                                      |             |      |       |    |    |    |    |    |   |   |   |   |   |   |   |   |   |        |

| Reset: 0x0000000           Offset: 0x0200                                                                                              |             |      |       |    |    |    |    |    |   |   |   |   |   |   |   |   |   |        |

| Name        | Description                                       | Bits       | Access |

|-------------|---------------------------------------------------|------------|--------|

| -           | Reserved, read O                                  | Bit: 31:19 | RO     |

| IGNORE_VLAN | Make no VLAN check at all (overrules VLAN)        | Bit: 18    | RW     |

| VLAN        | Check VLAN against specified in Reg (else 0xABB8) | Bit: 17    | RW     |

| -           | Reserved, read O                                  | Bit: 16:1  | RO     |

| ENABLE      | Enable                                            | Bit: O     | RW     |

#### 3.2.3.2TSN Plugfest App Listener Delay Register

Delay from the Input Port to the PHY to the core. This is only required for internal timestamping.

| Tsn                                              | Tsn PlugfestAppListenerDelay Reg |      |    |    |    |    |    |    |    |    |    |    |       |       |      |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|--------------------------------------------------|----------------------------------|------|----|----|----|----|----|----|----|----|----|----|-------|-------|------|-----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| Reg                                              | Descrip                          | tion |    |    |    |    |    |    |    |    |    |    |       |       |      |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| 31                                               | 30 29                            | 28   | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17    | 16    | 15   | 14  | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|                                                  |                                  |      |    |    |    |    |    |    |    |    |    |    |       |       |      |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|                                                  |                                  |      |    |    |    |    |    |    |    |    |    |    |       |       |      |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|                                                  |                                  |      |    |    |    |    |    |    |    |    |    |    |       |       |      |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|                                                  |                                  |      |    |    |    |    |    |    |    |    |    |    |       |       | ≻    |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| $\vdash {} {} {} {} {} {} {} {} {} {} {} {} {} $ |                                  |      |    |    |    |    |    |    |    |    |    |    |       |       |      |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|                                                  |                                  |      |    |    |    |    |    |    |    |    |    |    |       |       |      |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|                                                  |                                  |      |    |    |    |    |    |    |    |    |    |    |       | L     | _    |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|                                                  |                                  |      |    |    |    |    |    |    |    |    |    |    |       |       |      |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|                                                  |                                  |      |    |    |    |    |    |    |    |    |    |    |       |       |      |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|                                                  |                                  |      |    |    |    |    |    |    |    |    |    |    |       |       |      |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|                                                  |                                  |      |    |    |    |    |    |    |    |    |    | Г  | Docot | R\    |      |     |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|                                                  |                                  |      |    |    |    |    |    |    |    |    |    | F  |       | : 0x0 |      |     | 0  |    |    |    |   |   |   |   |   |   |   |   |   |   |

|                                                  |                                  |      |    |    |    |    |    |    |    |    |    |    | Of    | fset: | 0x0. | 210 |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Name  | Description                                                                        | Bits      | Access |

|-------|------------------------------------------------------------------------------------|-----------|--------|

| DELAY | RX Delay in Nanoseconds, used needed for internal timestamp compensation when used | Bit: 31:0 | RW     |

#### 3.2.3.3TSN Plugfest App Listener VLAN Register

VLAN to check if VLAN check is enabled and not the default one shall be used or VLAN check shall be ignored.

| 31       30       29       28       27       26       25       24       23       22       21       20       19       18       17       16       15       14       13       12       11       10       9       8       7       6       5       4       3       2       1       0         30       29       28       27       26       25       24       23       22       21       20       19       18       17       16       15       14       13       12       11       10       9       8       7       6       5       4       3       2       1       0 | Tsn PlugfestAppListenerVlan Reg |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| RO RO RW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Reg Description                 |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| RO RW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 31 30                           | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| RO RW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                 |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| RO RW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                 |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

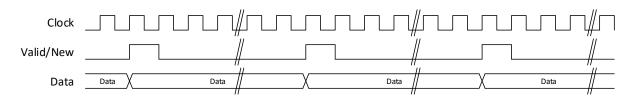

| RO RW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                 |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |