# **TodSlaveClock**

A low-footprint, highly configurable, 100% hardware only NMEA/UBX/TSIP Time of Day (ToD) Slave Clock solution, specifically designed for high-performance distributed systems. Allows standalone synchronization via NMEA/UBX/TSIP messages from a NMEA/UBX/TSIP source e.g. GPS receivers via UART. All frame parsing and calculations are done completely in hardware.

### Key Features:

- NMEA/UBX/TSIP/ESIP (ToD)

Slave Clock

- 100% hardware only solution

- Vendor independent

- Hardware frame parser

- Time, UTC, Spoofing, Jamming, Satellite Status Support

- Hardware time conversion

- Quality supervision

## Typical Applications:

- Legacy Networks

- Time converters

- Time serves with GNSS

- Substation automation

- Distributed data acquisition

- Test and measurement

- Etc.

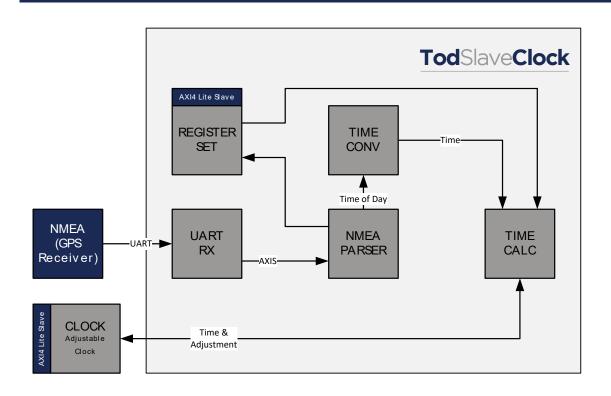

## IP Core Architecture:

## Specification:

NMEA Supports NMEA GxZDA, GxRMC, GxGSA, GxGSV, GxGGA and

GxUTC messages

Supports UBX NAV\_TIME\_UTC, NAV\_TIME\_LS, NAV\_STATUS,

MON\_HW and NAV\_SAT messages

Supports TSIP TIMING\_INFO, POSITION\_INFO, RECEIV-ER\_STATUS, SYSTEM\_ALARMS and SAT\_INFO messages

Supports ESIP CRW, CRY, CRJ messages

UTC handling and Status information for UBX/TSIP/ESIP

Hardware UART with configurable baud rate: 9.6k - 1m baud

Hardware conversion from time of day format to seconds since

midnight 1.1.1970 including leap years.

Hard time set to the parsed second plus configurable offset at

the second overflow of the local clock.

Performance Offload parsing, time format conversion and synchronization.

Portability 100% hardware only solution, no dependency on external CPU or

**UART**

Vendor independent, written in plain VHDL

Low footprint and low frequency requirements

Modularity Slim and standardized interfaces are used

Configuration No CPU required, standalone configuration with signals

Axi4 lite slave support, for status and configuration

#### Deliverables:

Ip core in plain VHDL

Testbench in plain VHDL

Reference Design with 1 PPS input and output

o Top level VHDL file

o Timing Constraint SDC files

o Vivado/Quartus Project file

## **Related Products:**

PPS Master/Slave

• PTP Ordinary Clock

• PTP Grandmaster Clock

PTP Hybrid Clock

IRIG Master/Slave

Adjustable Clock

• Signal Timestamper

Signal Generator